# **MS500**

Ultra-Low Power, Advanced Security, High Scalability DATASHEET

— Version 1.2

# **COPYRIGHT NOTICE**

Copyright © 2019 eWBM Co., Ltd. All rights reserved.

This document is the copyrighted work of eWBM Co., Ltd. and is owned by eWBM Co., Ltd. It is provided as a reference for the sole purpose of MS500 microcontroller based system design.

No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of eWBM Co., Ltd.

#### **No Warranty Notice**

eWBM Co., Ltd. makes no warranty of any kind in regard to this material which is delivered to you as is, including, but not limited to, the implied warranties as to its accuracy or fitness for a specific purpose. Any use of this technical documentation or the information contained therein is at the risk of the user. eWBM Co., Ltd. shall not be liable for errors contained therein or for incidental consequential damages in connection with the furnishing, performance or use of the material.

The information contained in this document is subject to change without notice.

# TABLE OF CONTENTS

| COPYRI    | IGHT NOTICE                            | 2  |

|-----------|----------------------------------------|----|

| TABLE     | e of Contents                          |    |

| TABLE     | E LIST                                 | 5  |

| Figur     | RE LIST                                | 6  |

| Prefa     | ACE                                    | 7  |

| AUDIE     | ENCE                                   | 7  |

| Docι      | UMENT REVISION AND REFERENCE           | 8  |

| INTROD    | DUCTION                                | 9  |

| Over      | RVIEW                                  | 9  |

| Featu     | URES                                   | 9  |

| 1.        | Processor Core                         |    |

| 2.        | On-chip Memories                       |    |

| 3.        | Clock generator                        |    |

| 4.        | Power                                  |    |

| 5.        | Serial interface                       |    |

| 6.        | Digital Peripherals                    |    |

| 7.        | Security block (Hardware Crypto Block) |    |

| 8.        | Package information                    |    |

| BLOCK     | K DIAGRAM                              |    |

| PIN & P   | PACKAGE CONFIGURATION                  |    |

| PIN M     | Лар (Тор View)                         | 14 |

|           | AGE DIMENSION                          |    |

|           | DESCRIPTION                            |    |

| 1.        |                                        |    |

| Pin M     | ν<br>Λυιτιριεχίng Matrix               |    |

|           | IONAL DESCRIPTION                      |    |

|           |                                        |    |

|           | 1 Cortex-M0 Integration                |    |

| 1.        |                                        |    |

| 2.        |                                        |    |

| 3.        |                                        |    |

| 4.        |                                        |    |

|           | IORIES                                 |    |

| 1.        |                                        |    |

| 2.<br>3.  |                                        |    |

| -         |                                        |    |

| <i>4.</i> |                                        |    |

|           | r Modes                                | -  |

| 1.<br>МГМ |                                        |    |

|           | IORY MAP                               |    |

| _         | ER MANAGEMENT                          |    |

| 1.        | Power domain                           |    |

| 2.      | Power mode operation             |  |

|---------|----------------------------------|--|

| CLOCK   | S                                |  |

|         | Clock Generation Unit            |  |

| 1.      | 32                               |  |

| 2.      | Crystal                          |  |

| З.      | Internal High-Speed Clock Source |  |

| 4.      | InternaL Low-Speed Clock Source  |  |

| 5.      | PLL                              |  |

| 6.      | Always-On Clock Generation Unit  |  |

| Reset.  |                                  |  |

| 1.      | RESET GENERATION DIAGRAM         |  |

| 2.      | RESET SOURCES                    |  |

| З.      | RESET GENERATION STRUCTURE       |  |

| 4.      | RESET GENERATION SIGNAL          |  |

| Systen  | M CONTROL                        |  |

| 1.      | System Control                   |  |

| Serial  | INTERFACES                       |  |

| 1.      | Quad SPI Flash Interface (spif)  |  |

| 2.      | SPI                              |  |

| З.      | <i>t</i> <sup>2</sup> <i>C</i>   |  |

| 4.      | UART                             |  |

| 5.      | SDMMC (Host Controller)          |  |

| 6.      | SDIO (Slave Controller)          |  |

| DIGITA  | AL PERIPHERALS                   |  |

| 1.      | DMA Controller                   |  |

| 2.      | Security Block                   |  |

| З.      | Watchdog Timer                   |  |

| 4.      | General-Purpose Timers           |  |

| 5.      | RTC                              |  |

| 6.      | General-Purpose I/O              |  |

| LECTRIC | CAL SPECIFICATIONS               |  |

| Absol   | UTE MAXIMUM RATES                |  |

| RECON   | IMENDED OPERATING CONDITIONS     |  |

| Power   | R CONSUMPTION                    |  |

| ELECTR  | RICAL CHARACTERISTICS            |  |

# TABLE LIST

| TABLE 1 SYSTEM CONFIGURATION PINS                                                               |     |

|-------------------------------------------------------------------------------------------------|-----|

| TABLE 2 PIN MUX MATRIX                                                                          |     |

| TABLE 3 NVIC INTERRUPTS                                                                         |     |

| TABLE 4 BOOT MODES SELECT BY THE EFUSE'S BIT (WHEN EFUSE 'S ADDRESS 0, BIT [2:0] PROGRAMMED)    |     |

| TABLE 5 BOOT MODES SELECTED BY BOOT PINS (WHEN EFUSE 'S ADDRESS 0, BIT[2:0] DOESN'T PROGRAMMED) | 23  |

| TABLE 6 MEMORY MAPPING                                                                          | 25  |

| TABLE 7 LOW POWER MODE AND POWER DOMAIN TABLE                                                   | 29  |

| TABLE 8 ENTRANCE OF LOW POWER MODE CONDITION                                                    | 29  |

| TABLE 9 WAKEUP CONDITION OF LOW POWER MODE                                                      | 30  |

| TABLE 10 POWER MANAGEMENT REGISTER DESCRIPTION                                                  | 30  |

| TABLE 11 MS500 RESET HIERARCHY                                                                  | 37  |

| TABLE 12 RESET GENERATION SIGNAL                                                                |     |

| TABLE 13 MS500 CLOCK/RESET MANAGER REGISTER DESCRIPTION                                         | 39  |

| TABLE 14 SYSCON REGISTER                                                                        |     |

| TABLE 15 QSPI REGISTER DESCRIPTION                                                              |     |

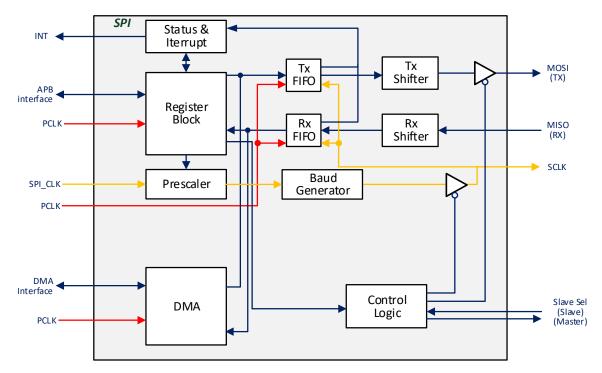

| TABLE 16. SPI OPERATING CLOCK MAPPING FREQUENCY                                                 | 57  |

| TABLE 17 SPI1, SPI2 REGISTER SUMMARY                                                            |     |

| TABLE 18 SPI1, SPI2 REGISTER DESCRIPTION                                                        | 60  |

| TABLE 19 SPI3 CONTROLLER REGISTER DESCRIPTION                                                   | 62  |

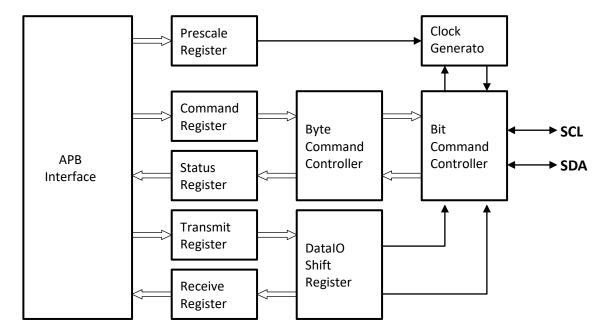

| TABLE 20 I <sup>2</sup> C REGISTER DESCRIPTION                                                  |     |

| TABLE 21 UART MEMORY MAP                                                                        | 71  |

| TABLE 22 UART REGISTER DESCRIPTION                                                              | 72  |

| TABLE 23 SDMMC HOST CONTROLLER REGISTER DESCRIPTION                                             | 81  |

| TABLE 24 MEMORY MAPPING OF SDIO REGISTERS                                                       | 88  |

| TABLE 25 DMA REQUEST SIGNAL MAPPING                                                             | 89  |

| TABLE 26 DMA REQUEST SELECT TO REQ9/10/11                                                       |     |

| TABLE 27 DMA REGISTER SUMMARY                                                                   |     |

| TABLE 28 DMA REGISTER DESCRIPTION                                                               | 91  |

| TABLE 29 WATCHDOG TIMER REGISTER DESCRIPTION                                                    |     |

| TABLE 30 GENERAL-PURPOSE DUAL TIMER REGISTER DESCRIPTION                                        | 101 |

| TABLE 31 RTC REGISTER DESCRIPTION                                                               |     |

| TABLE 32 GPIO REGISTER SUMMARY                                                                  |     |

| TABLE 33 ABSOLUTE MAXIMUM RATINGS FOR MS500                                                     | 112 |

| TABLE 34 RECOMMENDED OPERATING CONDITIONS FOR MS500                                             | 112 |

| TABLE 35 RUN/ACTIVE MODE CURRENT CONSUMPTION(1.8V)                                              |     |

| TABLE 36 RUN/ACTIVE MODE CURRENT CONSUMPTION(3.3V)                                              |     |

| TABLE 37 LPM0/LPM1/LPM2 MODE CURRENT CONSUMPTION(1.8V)                                          |     |

| TABLE 38 LPM0/LPM1/LPM2 MODE CURRENT CONSUMPTION(3.3V)                                          |     |

| TABLE 39 STANDBY MODE (LPM3) MODE CURRENT CONSUMPTION(1.8V)                                     |     |

| TABLE 40 STANDBY MODE (LPM3) MODE CURRENT CONSUMPTION(3.3V)                                     |     |

| TABLE 41 STANDBY MODE (LPM3) CURRENT CONSUMPTION FOR LORA APPLICATION                           |     |

| TABLE 42 ELECTRICAL SPECIFICATION                                                               | 117 |

# **FIGURE LIST**

| FIGURE 1 MS500 BLOCK DIAGRAM                                         |     |

|----------------------------------------------------------------------|-----|

| FIGURE 2 MS500 PIN MAP (TOP VIEW)                                    |     |

| FIGURE 3 MS500 PACKAGE VIEW (TOP VIEW)                               | 15  |

| FIGURE 4 MS500 PACKAGE VIEW (BOTTOM VIEW)                            | 15  |

| FIGURE 5 MS500 PACKAGE VIEW (SIDE VIEW)                              | 15  |

| FIGURE 6 INSTRUCTION CACHE BLOCK DIAGRAM                             | 22  |

| FIGURE 7 POWER MODE OPERATION                                        |     |

| FIGURE 8 MS500 CLOCK GENERATION                                      |     |

| FIGURE 9 RESET GENERATION BLOCK DIAGRAM                              |     |

| FIGURE 10 SPI BLOCK DIAGRAM                                          | 58  |

| FIGURE 11 FSM                                                        |     |

| Figure 12 I <sup>2</sup> C Block Diagram                             | 66  |

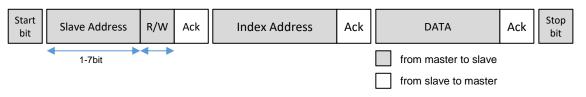

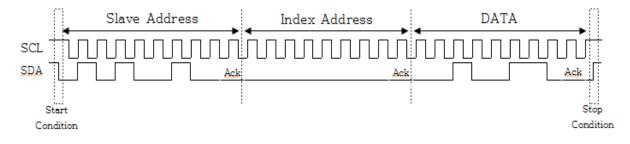

| FIGURE 13 I2C DATA TRANSFER                                          | 67  |

| FIGURE 14 THE FOLLOWING WAVEFORM SHOWS A TYPICAL I2C MASTER TRANSFER |     |

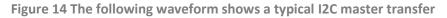

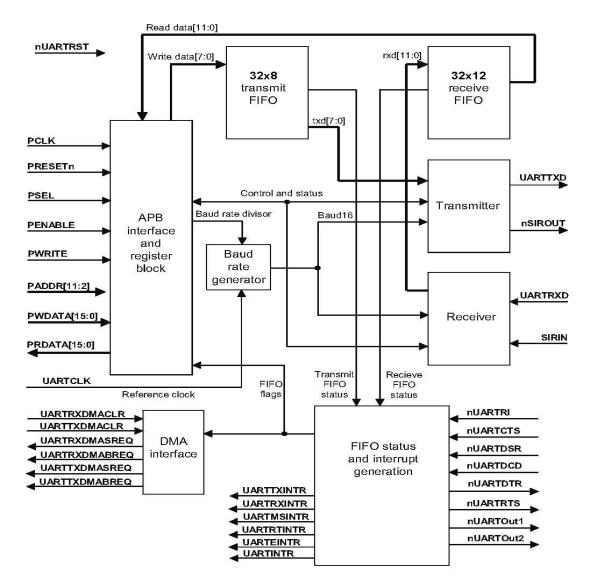

| FIGURE 15 UART BLOCK DIAGRAM                                         | 71  |

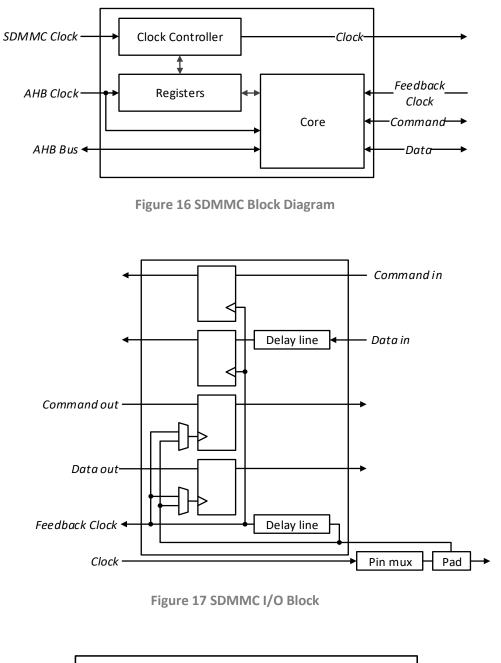

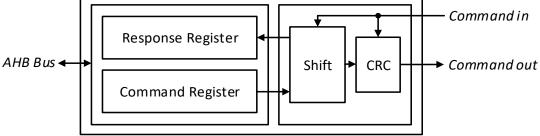

| FIGURE 16 SDMMC BLOCK DIAGRAM                                        | 80  |

| FIGURE 17 SDMMC I/O BLOCK                                            |     |

| FIGURE 18 SDMMC COMMAND PATH                                         |     |

| FIGURE 19 WDT OPERATION TIMING DIAGRAM                               |     |

| FIGURE 20 TIMER BLOCK DIAGRAM                                        | 100 |

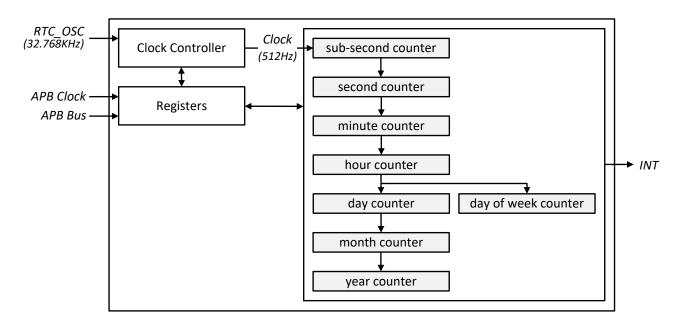

| FIGURE 21 RTC BLOCK DIAGRAM                                          | 103 |

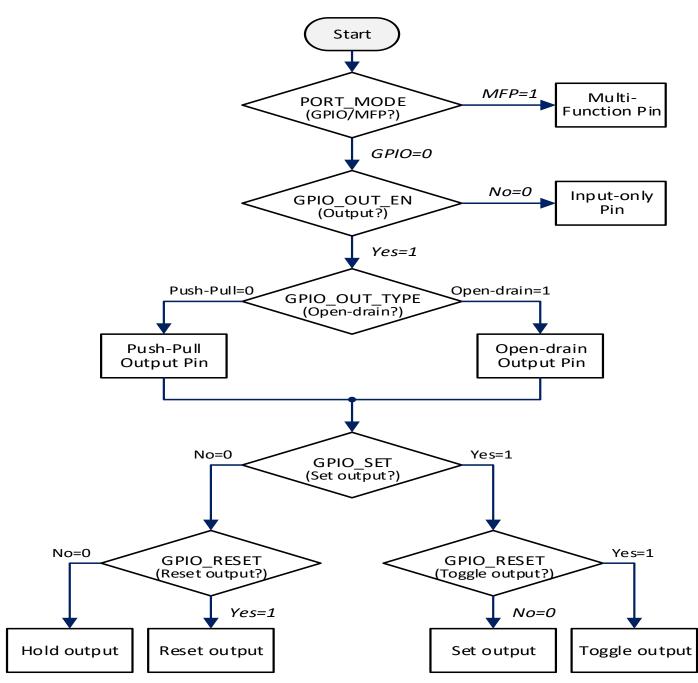

| FIGURE 22 GPIO PIN CONTROL                                           | 108 |

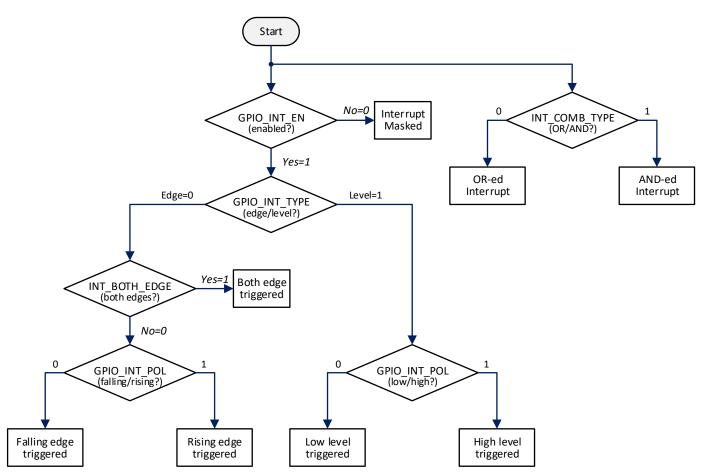

| FIGURE 23 GPIO INTERRUPT REGISTER                                    | 109 |

## PREFACE

This datasheet provides reference information for the MS500 microcontroller, describing the functional blocks of the system-on-chip (SoC) device designed around the ARIM<sup>®</sup> Cortex<sup>™</sup>-IVI0 core.

The purpose of this book is to provide working knowledge of the MS500 microcontroller.

Using this foundation, the reader will be equipped to understand and implement the MS500 microcontroller features. For better understanding of MS500, the major technical concepts of the MS500 are selected and introduced gradually over several chapters with preactical examples supporting theory.

## AUDIENCE

This book is intended for system software developers, hardware designers, and application developers.

# **DOCUMENT REVISION AND REFERENCE**

# **Revision History**

| Revision | Date        | Description                                                                   |

|----------|-------------|-------------------------------------------------------------------------------|

| 1.0      | 22-Aug-2016 | 1 <sup>st</sup> Release                                                       |

| 1.01     | 12-Dec-2016 | RTC register added / SDIO Slave added                                         |

| 1.02     | 13-Dec-2016 | Detail describe Boot mode / Correction typing errors                          |

| 1.03     | 15-Dec-2016 | Add PMU(power management unit) description                                    |

| 1.04     | 29-Dec-2016 | Add Power consumption table                                                   |

| 1.05     | 03-Jan-2017 | Add syscon register & power table classified                                  |

| 1.06     | 12-Jan-2017 | Correction PMU(LPM3) wakeup condition                                         |

| 1.07     | 24-Jan-2017 | Correction BKSRAM mode register                                               |

| 1.08     | 06-Apr-2017 | Match Table 2 and package pin map (PC12~PC15 deleted)                         |

| 1.09     | 10-May-2017 | Table 17 updated (I2C)                                                        |

| 1.10     | 24-May-2017 | Update Figure 1 / Add Flash memory density (4MB)                              |

| 1.11     | 09-Sep-2017 | Correction Table 36 comments                                                  |

| 1.12     | 24-Nov-2017 | Correction BOOT_SRC register                                                  |

| 1.13     | 01-Feb-2018 | Change SPI3 operation mode                                                    |

| 1.14     | 06-Mar-2018 | Update Block Diagram/Add Crystal operation condition and change register name |

|          |             | (STBY_WU_REC -> LPM_WU_REC) on the syscon part                                |

| 1.15     | 02-Apr-2018 | Update Pin & package configuration and PAD name change                        |

| 1.2      | 30-May-2019 | Add LoRa Application info                                                     |

# **INTRODUCTION**

## **OVERVIEW**

The MS500 is an ARM<sup>®</sup> Cortex-M0<sup>™</sup> based RISC microcontroller with Hardware Security Block for embedded applications featuring a high level of integration and low-power consumption.

The MS500 operates at CPU frequency up to 100MHz. The MS500 features a security block called Crypto Block. The Crypto Block consists of Asymmetric Crypto Accelerator (ACA), Symmetric Crypto Accelerator (SCA), and TRNG (True Random Number Generator). It protects the device and its data at boot time, run time and during the communication with other devices or with the cloud.

The peripheral complement of the MS500 includes up to 64 KB of internal SRAM, 8 KB Boot ROM, 4MB Internal flash memory, Non-volatile eFuse memory, Quad SPI interface (SPIF), three SPI controllers, 2-channel DMA controller, two General Purpose Timers, Watchdog Timer, SDMMC interface, three UARTs, four I2Cs, and up to 41 fast general purpose I/O pins.

With its security features as well as low-power, high performance, and diverse connectivity options., the MS500 is ideal for IoT applications such as Smart home applications, Smart metering, Tele-monitoring, Remote Healthcare, and other Electronic devices linked to the Internet.

## **FEATURES**

#### 1. PROCESSOR CORE

- 32-bit hardware multiplier providing Up to 100 MHz operation frequency.

- Built-in Nested Vectored Interrupt Controller (NVIC) for fast deterministic interrupt processing.

- Wake-up Interrupt Controller (WIC) allows automatic wake from any priority interrupt at ultra-low power sleep mode support

- AMBA AHB-Lite Interface

- System Tick Timer.

- 8KB Level 1, 4 way set-associative Instruction Cache for XIP (execute in place).

#### 2. ON-CHIP MEMORIES

- 64 KB SRAM for general purpose such as data buffer supporting security and non-security access

- 8 KB Boot ROM, supporting system code downloaded by UART interface

- 1024 bits Non-Volatile e-Fuse providing storage for the secret keys.

- 4MB (32Mbits) flash Memory

#### 3. CLOCK GENERATOR

- Embedded 32KHz Low-speed Internal RC oscillator for Ultra low power mode.

- Embedded 6~15 MHz RC oscillator allowing operation without external Oscillator or external Crystal. (User Selectable)

- Internal PLL for high frequency clock generation.

- One oscillator with 24MHz clock input and embedded PLLs

- Support global soft-reset control for entire SOC, or individual soft-reset for every components

#### 4. POWER

- Single 3.3V (1.7V~3.6V) power supply with on-chip internal voltage regulator for the core supply and the always-on (AON) power domain.

- Three Low-power modes.: Sleep, Deep-sleep, Standby.

- Built-in Brown-out detection (BOD) circuit for monitoring 3 supply voltage levels.

- Power-on Reset (POR).

- Power Management Unit (PMU) to minimize power consumption during {Sleep} mode.

#### 5. SERIAL INTERFACE

- Quad SPI Flash Interface (SPIF) with 1-, 2- and 4-bit data at rate of up to 50MB per second.

- Three UARTs supporting for DMA and full modem control.

- Four I<sup>2</sup>C bus interfaces supporting for DMA, master and slave operations, Fast mode plus with data rates of up to 400kbit/s.

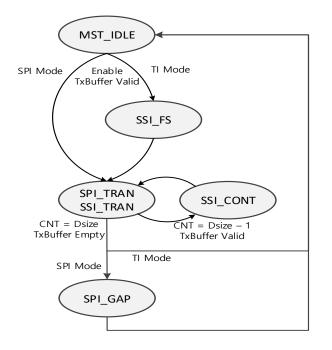

- Three SPI controllers; One SPI controller and two SSP controllers supporting FIFO, multi-protocols, DMA, and master and slave operations.

- Support three chip-selects output, serial-master and serial-slave mode, and software configurable.

#### 6. DIGITAL PERIPHERALS

- 2-channel Direct Memory Access (DMA) controller which can access all memories on the AHB-lite and all peripherals which have DMA support.

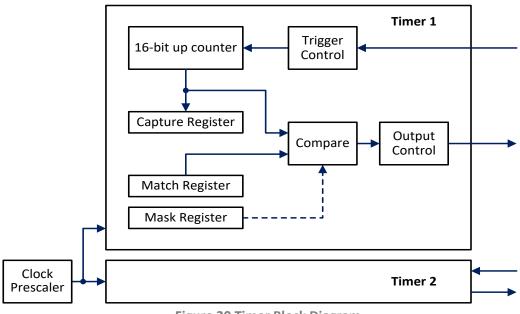

- Two 2-channel General Purpose Timers.

- Programmable Watchdog Timer.

- Ultra-low power Real-Time Clock (RTC).

- SDMMC card interface with support for eMMC 4.41, SD 3.01 and SDIO 3.0 Host controller.

- SDIO 3.0 Slave controller.

- Up to 41 Fast GPIO pins with configurable.

#### 7. SECURITY BLOCK (HARDWARE CRYPTO BLOCK)

- Asymmetric Crypto Accelerator (ACA)

- Features:

- Offloads public key cryptography processing.

- · RSA up to 2048 bit private/public keys

- ECC up to 512 bit private/public keys

- Symmetric Crypto Accelerator (SCA)

SCA provides a framework including a programmable sequencer, DMA engine, and cryptographic/hashing resources that may handle a variety of protocols involving a cipher and a hash. Also, SCA optimizes cryptographic offload for bulk processing of block cipher and hash algorithms.

- Features:

- · AES128/256(ECB, CBC, CTR, CCM, GCM Modes),

- SHA1/SHA256 (HASH and HMAC modes)

- · ARIA 128/192/256

- DMA provides processor offload

TRNG (True Random Number Generator)

The TRNG generates random data that is intended to be statistically equivalent to a uniformly distributed random data stream.

- Features:

- · Complies NIST SP 800-90a/b/c.FIPS 140-2 and FIPS 140-3 (draft).

- High speed operation

- 25Mbps at 100MHz

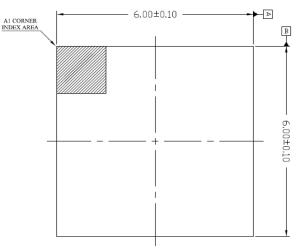

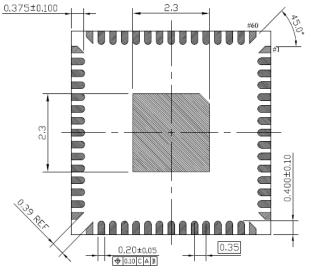

#### 8. PACKAGE INFORMATION

- 60-pin LGA

- Ball Pitch: 0.35 mm

- **Package Width**  $\times$  Length : 6 mm  $\times$  6 mm

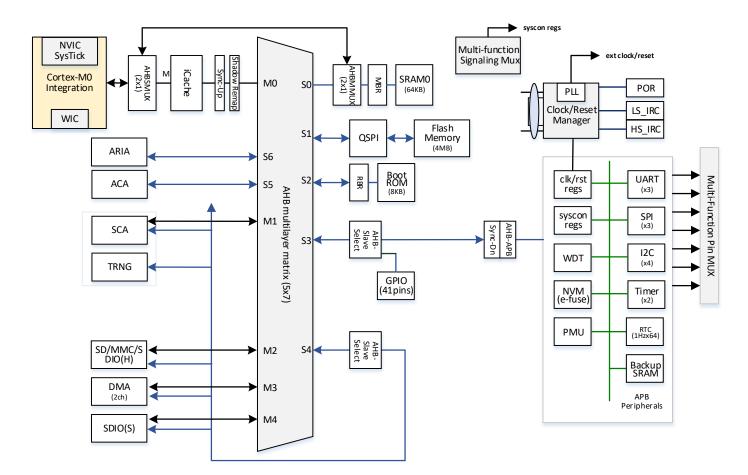

# **BLOCK DIAGRAM**

The following subsections provides an architectural overview of the MS500.

Figure 1 MS500 Block Diagram

# **PIN & PACKAGE CONFIGURATION**

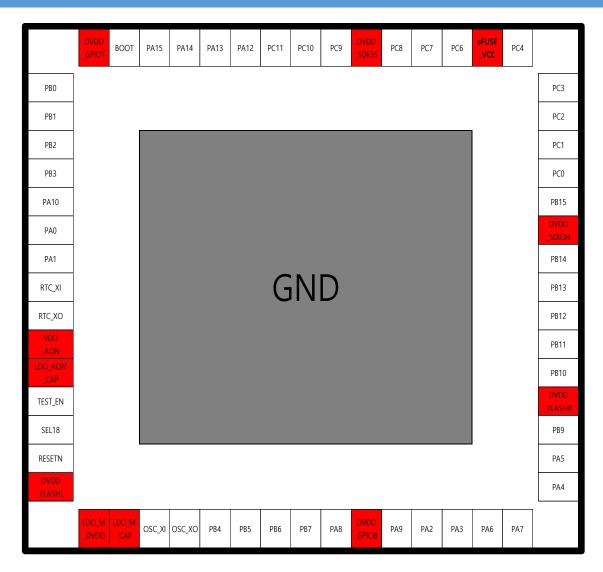

# PIN MAP (TOP VIEW)

Figure 2 MS500 Pin Map (Top View)

# PACKAGE DIMENSION

Figure 3 MS500 Package View (TOP VIEW)

Figure 4 MS500 Package View (BOTTOM VIEW)

Figure 5 MS500 Package View (SIDE VIEW)

# **PIN DESCRIPTION**

## **1. SYSTEM CONFIGURATION PINS**

Table 1 System Configuration Pins

| Pin                                                                         | Description                                                                             |  |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| OSC_XI Crystal oscillator XI for system operation, Recommend 24MHz or 12MHz |                                                                                         |  |  |  |  |

| OSC_XO Crystal oscillator XO for system operation, Recommend 24MHz or 12MHz |                                                                                         |  |  |  |  |

| RTC_XI RTC oscillator XI for Real time clock only(option), use 32.768KHz    |                                                                                         |  |  |  |  |

| RTC_XO                                                                      | RTC oscillator XO for Real time clock only(option), use 32.768KHz                       |  |  |  |  |

| TEST_EN                                                                     | Chip test mode enable only, Tie to GND when normal operation                            |  |  |  |  |

| BOOT Boot mode bit 0                                                        |                                                                                         |  |  |  |  |

| PA6(Boot1) Boot mode bit 1 when reset release                               |                                                                                         |  |  |  |  |

| PA7(Boot2) Boot mode bit 2 when reset release                               |                                                                                         |  |  |  |  |

| SEL18                                                                       | Select VDDIO voltage range (input 0 : IO voltage is 3.3V, input 1 : IO voltage is 1.8V) |  |  |  |  |

| RESETN                                                                      | Chip reset (Active Low)                                                                 |  |  |  |  |

| PA0                                                                         | Wake up signal input to wake up from standby mode (Active High)                         |  |  |  |  |

| PA1 When MS500 go to standby mode, this pin output HIGH                     |                                                                                         |  |  |  |  |

# PIN MULTIPLEXING MATRIX

Table2 shows the pin mux matrix of the MS500, GPIO\_i means GPIO input mode.

#### Table 2 Pin Mux Matrix

| PinDeterPA0WAKEPA1STANDPA2GPI0PA3TD0_TRA | BY_O<br>D_i<br>KCESWO TDO_TRACE |             | (UART)     | (I2C)    | (TIMER)     | (SDMMC)     |

|------------------------------------------|---------------------------------|-------------|------------|----------|-------------|-------------|

| PA1 STAND<br>PA2 GPI                     | BY_O<br>D_i<br>KCESWO TDO_TRACE |             |            |          |             |             |

| PA2 GPI                                  |                                 |             |            |          |             |             |

|                                          | CESWO TDO_TRACE                 |             |            |          |             |             |

| PA3 TDO_TRA                              |                                 |             |            | I2C3_SCL |             | SDIO_PULLUP |

|                                          |                                 | SWO         |            | I2C3_SDA |             |             |

| PA4 GPI                                  |                                 |             |            | I2C2_SCL |             |             |

| PA5 GPI                                  | D_i                             |             |            | I2C2_SDA |             |             |

| <b>PA6</b> BOO                           | T[1] BOOT[1]                    |             |            |          |             |             |

| PA7 BOO                                  | T[2] BOOT[2]                    |             |            |          |             |             |

| PA8 GPI                                  | D_i EXTOUT_C                    | _K1         | UART1_TX   |          |             |             |

| PA9 GPI                                  | D_i EXTOUT_C                    | LK2         | UART1_RX   |          |             |             |

| PA10 WAKE                                | UP[1] WAKEUP[                   | 1]          | UART1_RTSN |          |             |             |

| <b>PA12</b> TCK_S                        | WCLK TCK_SWC                    | LK SSP2_SCK | UART2_RTSN |          |             |             |

| PA13 TMS_S                               | wdio tms_swd                    | IO SSP2_SSN | UART2_CTSN |          |             |             |

| <b>PA14</b> TC                           | DI TDI                          | SSP2_MISO   | UART3_RTSN |          |             |             |

| PA15 TRS                                 | TN TRSTN                        | SSP2_MOSI   | UART3_CTSN |          |             |             |

| PBO GPI                                  | D_i                             | SSP1_SCK    |            | I2C4_SCL | TMR2_MAT[2] |             |

| PB1 GPI                                  | D_i                             | SSP1_SSN    |            | I2C4_SDA | TMR2_CAP[2] |             |

| PB2 GPI                                  | D_i                             | SSP1_MISO   |            | I2C1_SCL | TMR2_MAT[1] |             |

| PB3 GPI                                  | D_i                             | SSP1_MOSI   |            | I2C1_SDA | TMR2_CAP[1] |             |

| PB4 GPI                                  | D_i                             | SSP3_SCK    | UART2_TX   |          |             |             |

| PB5 GPI                                  | D_i                             | SSP3_SSN    | UART2_RX   |          |             |             |

| PB6 GPI                                  | D_i                             | SSP3_MISO   | UART3_TX   | I2C2_SCL |             |             |

| PB7 GPI                                  | D_i                             | SSP3_MOSI   | UART3_RX   | I2C2_SDA |             |             |

| PB9 GPI                                  | D_i                             |             |            | I2C1_SDA |             |             |

| PB10 GPI                                 | D_i                             |             |            |          |             | SDHC_CLK    |

| PB11 GPI                                 | D_i                             | SSP1_SCK    |            |          |             | SDHC_CMD    |

| PB12 GPI                                 | D_i                             | SSP1_SSN    |            |          |             | SDHC_DAT[0] |

| PB13 GPI                                 | D_i                             | SSP1_MISO   |            |          |             | SDHC_DAT[1] |

| PB14 GPI                                 | D_i                             | SSP1_MOSI   |            |          |             | SDHC_DAT[2] |

| PB15 GPI                                 | D_i                             |             |            |          |             | SDHC_DAT[3] |

| PC0 GPI                                  | D_i                             | SSP2_SCK    |            |          |             | SDHC_DAT[4] |

| PC1 GPI                                  | D_i                             | SSP2_SSN    |            |          |             | SDHC_DAT[5] |

| PC2  | GPIO_i | SSP2_MISO |          | SDHC_DAT[6] |

|------|--------|-----------|----------|-------------|

| PC3  | GPIO_i | SSP2_MOSI |          | SDHC_DAT[7] |

| PC4  | GPIO_i |           | SDHC_CDN | eMMC_RSTn   |

| PC6  | GPIO_i |           |          | SDIO_CLK    |

| PC7  | GPIO_i |           |          | SDIO_CMD    |

| PC8  | GPIO_i | SSP3_SCK  |          | SDIO_DAT[0] |

| PC9  | GPIO_i | SSP3_SSN  |          | SDIO_DAT[1] |

| PC10 | GPIO_i | SSP3_MISO |          | SDIO_DAT[2] |

| PC11 | GPIO_i | SSP3_MOSI |          | SDIO_DAT[3] |

|      |        |           |          |             |

# **FUNCTIONAL DESCRIPTION**

## **ARM CORTEX-MO INTEGRATION**

The ARM Cortex-M0 is a 32-bit microprocessor with a simple, easy-to-use programmers model and excellent code density, designed for low-power operation and high performance interrupt handling.

#### 1. ARM CORTEX-M0 PROCESSOR

The ARM Cortex-M0 incorporates a 3-stage pipeline von Neumann architecture with separate buses for instruction cache, data sync-up cache, and cache of shadow remap, making it ideal for demanding embedded application. The Cortex-M0 processor also implements the ARMv6-M architecture, which is based on the 16-bit Thumb instruction set that provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers. In addition, Cortex-M0 closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance

#### 2. NESTED VECTORED INTERRUPT CONTROLLER (NVIC)

The NVIC and the processor core interface are tightly coupled to enable low interrupt latency and efficient processing of late arriving interrupts. It includes 32 interrupt inputs and a Wakeup Interrupt Controller (WIC) When the main processor is in Deep Sleep mode the WIC can wake up the processor. This allows the power to be switched off to the main processor when it is not in use.

| Posi<br>tion | Prio<br>rity | Type of<br>priority | Acronym | Description                                                                   | Address     |

|--------------|--------------|---------------------|---------|-------------------------------------------------------------------------------|-------------|

| 0            | 7            | settable            | syscon  | System Int<br>(Clock Status, WAKEUP pin), plus event which can be used as NMI | 0x0000 0040 |

| 1            | 8            | settable            | RTC     | RTC (alarm or wakeup)                                                         | 0x0000 0044 |

| 2            | 9            | settable            | DMA     | DMA IRQ                                                                       | 0x0000 0048 |

| 3            | 10           | settable            | DMA     | DMA Error IRQ                                                                 | 0x0000 004C |

| 4            | 11           | settable            | SDIO    | SDIO global interrupt                                                         | 0x0000 0050 |

| 5            | 12           | settable            | SDMMC   | SDMMC global interrupt                                                        | 0x0000 0054 |

| 6            | 13           | settable            | TRNG    | Security Module (TRNG)                                                        | 0x0000 0058 |

#### Table 3 NVIC Interrupts

| 7  | 14 | settable | ARIA          | ARIA interrupt                | 0x0000 005C |

|----|----|----------|---------------|-------------------------------|-------------|

| 8  | 15 | settable | SCA           | Security Engine (SCA)         | 0x0000 0060 |

| 9  | 16 | settable | Reserved      |                               | 0x0000 0064 |

| 10 | 17 | settable | ACA           | ACA global Interrupt          | 0x0000 0068 |

| 11 | 18 | settable | clk_reset_mgr | Clock reset manager interrupt | 0x0000 006C |

| 12 | 19 | settable | WatchDog      | WDT interrupt                 | 0x0000 0070 |

| 13 | 20 | settable | GPIO1         | GPIO1 global interrupt        | 0x0000 0074 |

| 14 | 21 | settable | GPIO2         | GPIO2 global interrupt        | 0x0000 0078 |

| 15 | 22 | settable | GPIO3         | GPIO3 global interrupt        | 0x0000 007C |

| 16 | 23 | settable | I2C1          | I2C1 global interrupt         | 0x0000 0080 |

| 17 | 24 | settable | I2C2          | I2C2 global interrupt         | 0x0000 0084 |

| 18 | 25 | settable | I2C3          | I2C3 global interrupt         | 0x0000 0088 |

| 19 | 26 | settable | I2C4          | I2C4 global interrupt         | 0x0000 008C |

| 20 | 27 | settable | SSP1          | SSP1 global interrupt         | 0x0000 0090 |

| 21 | 28 | settable | SSP2          | SSP2 global interrupt         | 0x0000 0094 |

| 22 | 29 | settable | SSP3          | SSP3 global interrupt         | 0x0000 0098 |

| 23 | 30 | settable | UART1         | UART1 global interrupt        | 0x0000 009C |

| 24 | 31 | settable | UART2         | UART2 global interrupt        | 0x0000 00A0 |

| 25 | 32 | settable | UART3         | UART3 global interrupt        | 0x0000 00A4 |

| 26 | 33 | settable | Timer1        | Timer1 global interrupt       | 0x0000 00A8 |

| 27 | 34 | settable | Timer2        | Timer2 global interrupt       | 0x0000 00AC |

| 28 | 35 | settable | Reserved      |                               | 0x0000 00B0 |

| 29 | 36 | settable | Reserved      |                               | 0x0000 00B4 |

| 30 | 37 | settable | Reserved      |                               | 0x0000 00B8 |

| 31 | 38 | settable | Reserved      |                               | 0x0000 00BC |

|    |    |          |               |                               |             |

#### 3. SYSTICK TIMER

The ARM Cortex-M0 processor has a 24-bit count-down timer. This can be configured as a Real Time Operating System (RTOS) tick timer or as a simple counter.

#### 4. BUS SYSTEM

The ARM Cortex-M0 processor within the MS500 implements the AHB-Lite bus interface for communication with internal memories and on-chip peripherals.

## MEMORIES

The MS500 contains boot ROM, on-chip SRAM and Non-volatile e-Fuse memory.

#### 1. BOOT ROM

The MS500 contains internal ROM memory which is used to store the boot code for the ARM Cortex-M0. When the ARM Cortex-M0 processor is released from reset, it immediately starts execution of the boot code stored in this ROM.

The size of ROM is 8 KB

#### 2. ON-CHIP SRAM

The MS500 contains 64 KB of on-chip SRAM which is used by the ARM Cortex-M0 for general purpose memory (stack, heap and data butters). Certain peripherals with DMA capability can also access this memory directly for high speed data processing.

#### 3. NON-VOLATILE MEMORY (NVM)

eFuse is a non-volatile one-time programmable memory used to permanently store device/system configuration settings, software-specific configuration information and user-defined information.

The eFuse memory also contains device specific information including device ID (DID), platform key (PFK), device unique key (DUK), and a user definable key. For details on how to program eFuse with customer specific information, please contact eWBM's technical support.

- 1024-bits high-density electrical Fuse.

- Can be programmed by eWBM for Customer with special condition.

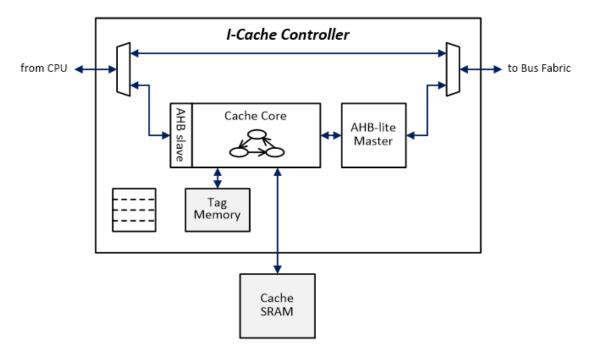

#### 4. INSTRUCTION CACHE

MS500 contains a special instruction cache to increase CPU performance when an application is executing directly from the flash memory connected to the QSPI (Quad SPI) flash interface.

The instruction cache has the following features:

- 8 KB cache memory

- 4-way set-associativity

- 64byte cache line size

- Provide zero-wait read cycle on cache hit

- Pseudo-LRU replacement policy

- Provide optional prefetching mode

- Up to 256MB of cacheable address space

Figure 6 Instruction Cache Block Diagram

# **BOOT MODES**

The MS500 supports various boot modes for both normal boot and secure boot. These modes can be selected by the internal eFuse boot configuration settings (Boot SRC[2:0]) as shown in table 4 or Boot mode pin as table5.

Boot\_SRC[2] Boot\_SRC[1] Boot\_SRC[0] **Boot Mode** Description Boot mode select by external boot mode pin **ROM Boot** 0 0 0 (Not programmed) UART2 to SRAM boot code download and boot from **UART-to-SRAM** 0 0 1 SRAM. The Dedicated pins are PB4/PB5. UART2 to Flash memory boot code download (using 0 **UART-to-Flash** 0 1 HS-IRC), and dedicated pins are PB4/PB5. SPI3 to SRAM boot code download and use HS-IRC SPI-to-SRAM 0 1 1 This is default, when eFuse bit does not programmed. (same boot\_src) The dedicated pins are PBO, PB1, PB2, PB3. eMMC to SRAM boot code download and use HS-IRC eMMC-to-SRAM To enable eMMC, it needs program dedicated eFuse 0 1 1 (same boot\_src) bits. (Address 0x1, bit [14:12] as 001) The eMMC Host pin use to this mode. Boot loading from internal SPI Flash memory directly. SPI Direct Boot1 1 0 0 (SPI 1-bit mode, using HS IRC) Boot loading from internal SPI Flash memory directly. SPI Direct Boot2 1 0 1 (SPI 4-bit mode, using XTAL) Boot loading from internal SPI Flash memory directly. SPI Direct Boot3 0 1 1 (SPI 4-bit mode, using HS\_IRC)

Table 4 Boot Modes select by the eFuse's bit(When eFuse 's address 0, bit[2:0] programmed)

If the Boot\_SRC[2:0] is set to 000, the default setting, then the external system pins (Boot [2:0]) are used to select the boot mode as shown in Table 6. This mean that boot Modes selected by boot pins.

Table 5 Boot Modes selected by boot pins (When eFuse 's address 0, bit[2:0] doesn't programmed)

| Boot Mode     | Boot[2] | Boot[1] | Boot[0] | Description                                                                                               |

|---------------|---------|---------|---------|-----------------------------------------------------------------------------------------------------------|

| ROM Boot      | 0       | 0       | 0       | Boot loading from ROM.                                                                                    |

| UART-to-SRAM  | 0       | 0       | 1       | UART2 to SRAM boot code download and boot from SRAM<br>The Dedicated pins are PB4/PB5.                    |

| UART-to-Flash | 0       | 1       | 0       | UART2 to Flash memory boot code download (SPI 4-bit mode, using HS-IRC) , and dedicated pins are PB4/PB5. |

Copyright - © 2019 eWBM Co., Ltd. All rights reserved

| SPI-to-SRAM<br>(same boot_src) | 0 | 1 | 1 | SPI3 to SRAM boot code download and use HS-IRC<br>This is default, when eFuse bit does not programmed.                                       |

|--------------------------------|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------|

| eMMC2SRAM<br>(same boot_src)   | 0 | 1 | 1 | eMMC to SRAM boot code download and use HS-IRC<br>To enable eMMC, it needs program dedicated eFuse bits<br>(Address 0x1, bit [14:12] as 001) |

| SPI Direct Boot1               | 1 | 0 | 0 | Boot loading from internal SPI Flash memory directly.(SPI 1-bit mode, using HS_IRC)                                                          |

| SPI Direct Boot2               | 1 | 0 | 1 | Boot loading from internal SPI Flash memory directly.(SPI 4-bit mode, using XTAL)                                                            |

| SPI Direct Boot3               | 1 | 1 | 0 | Boot loading from internal SPI Flash memory directly. (SPI 4-bit mode, using HS_IRC)                                                         |

#### **1. SECURE BOOT**

The MS500 is designed specifically to meet the need for the strong security in IoT devices by providing enhanced features such as secure boot, hardware protected secret keys and high performance hardware crypto modules.

The secure boot process is contained within the boot ROM. Once the secure boot has been enabled in the eFuse configuration bits, it cannot be modified and the main application will always be securely booted on power up. If the secure boot process fails, the MS500 will halt and not allow an invalid firmware application to execute.

The secure boot mode supported by the MS500 provides integrity check and authentication of the application firmware.

The boot ROM coordinates the SCA and ACA hardware modules to perform the secure boot process:

Step 1: the SCA hardware module performs SHA256 HMAC integrity check.

Step 2: the ACA hardware module performs an ECC verification of the HMAC to ensure authenticity.

# MEMORY MAP

The address map for the MS500 memory and peripherals are defined in Table 7.

**Table 6 Memory Mapping**

| Addr[31:28] | Name            | Start Addr              | End Addr    | Size | Brief Description        |

|-------------|-----------------|-------------------------|-------------|------|--------------------------|

| 0x0         | Shadow Region   | 0x0000_0000             | 0x0FFF_FFF  | 256M |                          |

| 0x1         | ROM             | 0x1FFF_E000             | Ox1FFF_FFF  | 8KB  | On-chip Boot Memory      |

|             | On-chip         | 0x2000_0000             | 0x2000_FFFF | 64K  | On-chip SRAM1            |

| 0x2         | Memory          | -                       | -           | -    | Reserved                 |

| 0x3         | QSPI            | 0x3000_0000             | 0x3FFF_FFFF | 256M | Flash memory             |

|             |                 | 0x4000_0000             | 0x4000_07FF | 2K   | System Control Register  |

|             |                 | 0x4000_0800             | 0x4000_0FFF | 2K   | NVM Control Register     |

|             |                 | 0x4000_1000             | 0x4000_1FFF | 4K   | Clock/Reset Manager      |

|             |                 | 0x4000_2000 0x4000_2FFF |             | 4K   | Watchdog Timer           |

|             |                 | 0x4000_3000             | 0x4000_37FF | 2K   | Timer1                   |

|             |                 | 0x4000_3800             | 0x4000_3FFF | 2К   | Timer2                   |

|             |                 | 0x4000_4000             | 0x4000_4FFF | 4K   | SPI1                     |

|             |                 | 0x4000_5000             | 0x4000_5FFF | 4K   | SPI2                     |

|             |                 | 0x4000_6000             | 0x4000_6FFF | 4K   | UART1                    |

|             | APB1 Peripheral | 0x4000_7000             | 0x4000_7FFF | 4K   | UART2                    |

|             |                 | 0x4000_8000             | 0x4000_8FFF | 4K   | 12C1                     |

| 0.4         |                 | 0x4000_9000             | 0x4000_9FFF | 4K   | 12C2                     |

| 0x4         |                 | 0x4000_A000             | 0x4000_AFFF | 4K   | 12C3                     |

|             |                 | 0x4000_B000             | 0x4000_BFFF | 4K   | 12C4                     |

|             |                 | 0x4000_C000             | 0x4000_CFFF | 4K   | SSP3                     |

|             |                 | 0x4000_D000             | 0x4000_DFFF | 4K   | UART3                    |

|             |                 | 0x4000_E000             | 0x4000_EFFF | 4K   | PMU                      |

|             |                 | 0x4000_F000             | 0x4000_F7FF | 2К   | RTC                      |

|             |                 | 0x4000_F800             | 0x4000_FFFF | 2К   | Backup SRAM(64x32bit)    |

|             | AHB Peripheral  | 0x4002_0000             | 0x4002_0FFF | 4K   | GPIO1 (16 I/Os)          |

|             |                 | 0x4002_1000             | 0x4002_1FFF | 4K   | GPIO2 (16 I/Os)          |

|             |                 | 0x4002_2000             | 0x4002_2FFF | 4K   | GPIO3 (16 I/Os)          |

|             |                 | -                       | -           | -    | Reserved                 |

|             | Reserved        | -                       | -           | -    | -                        |

|             |                 | 0x5000_0000             | 0x5000_0FFF | 4K   | DMA                      |

|             |                 | 0x5000_1000             | 0x5000_1FFF | 4K   | Reserved                 |

|             |                 | 0x5000_2000             | 0x5000_2FFF | 4K   | Reserved                 |

|             |                 | 0x5000_3000             | 0x5000_3FFF | 4K   | SD/MMC/SDIO Host         |

| <b>О</b> Г  | AHB Controller  | 0x5000_4000             | 0x5000_4FFF | 4K   | SD/SDIO Slave Controller |

| 0x5         |                 | 0x5000_5000             | 0x5000_5FFF | 4K   | SDIO CIS slave(128Words) |

|             |                 | 0x5000_6000             | 0x5000_6FFF | 4K   | Security Module (TRNG)   |

|             |                 | 0x5000_7000             | 0x5000_7FFF | 4K   |                          |

|             |                 | -                       | -           | -    | Reserved                 |

|             |                 | 0x5001_0000             | 0x5001_FFFF | 64K  | SCA                      |

|             |                 |                         |             |      |                          |

Copyright - © 2019 eWBM Co., Ltd. All rights reserved

|         |            | -           | -           | -   | Reserved              |

|---------|------------|-------------|-------------|-----|-----------------------|

|         | Reserved   | -           | -           | -   | -                     |

| 0.6     | AHB        | 0x6000_0000 | 0x6000_7FFF | 32K | ACA                   |

| 0x6     | Reserved   | -           | -           | -   | -                     |

| 0x7     | AHB        | 0x7000_0000 | 0x7000_7FFF | 32K | ARIA                  |

|         | Reserved   | -           | -           | -   | -                     |

| 0x8~0xD | Reserved   | -           | -           | -   | -                     |

| OxE     | Contour MO | 0xE000_0000 | 0xE00F_FFFF | 1M  | Cortex-M0 Private Bus |

|         | Cortex-M0  | -           | -           | -   | Reserved              |

| 0xF     | Cache      | 0xFFFF_F000 | 0xFFFF_FFFC | 4K  | Cache                 |

## **POWER MANAGEMENT**

#### **1. POWER DOMAIN**

The MS500 has two power domains, Always-on power domain which must always be supplied with power for normal operation, and Main power domain which can be turned on or off, independent of the Always on power domain. When the Main power domain power is off, the MS500 will be in standby mode and consume minimal power. To allow for standby mode to be enabled, separate power supplies should be connected to the external VDD\_AON (Always-On power supply) and LDO\_M\_DVDD (Main power supply) pins or the same power is supplied to VDD\_AON and LDO\_M\_DVDD. When same power is supplied, PMU(Power Management Unit) can shut-down LDO\_M and enter standby mode.

The MS500 provides assurance that the required voltage levels are met for each respective mode. If the voltage level is not correct for a specific mode, such as power on reset (POR), the MS500 will perform one of the following actions:

- delay entry into that mode until the correct voltage level is available

- generate a reset (brown-out detection (BOD))

Transitions between these modes are managed by the power management unit which response to CPU command.

The MS500 supports the following power modes in the order from highest to lowest power consumption:

- Active mode

- Sleep mode

- stops the processor clock

- System power-down modes;

- Deep-sleep mode stops the system clock and peripheral clock

- Turn off peripheral power

- Alive Always-On domain only

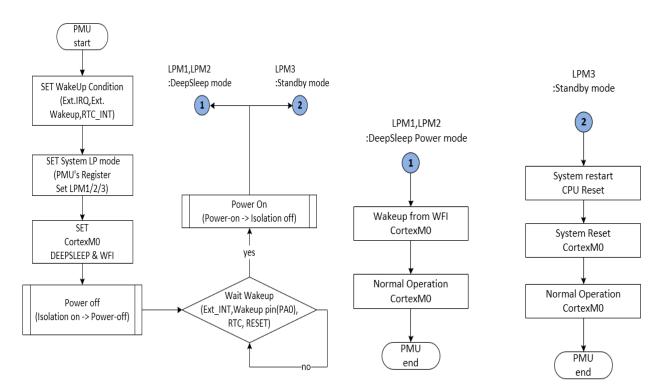

#### 2. POWER MODE OPERATION

The MS500 has active mode, sleep mode(LPM1, LPM2) and standby mode(LPM3). For the low power operation, CPU can function module power on/off control in the active mode. The LPM1,LPM2, LPM3 mode define which module on and off and this can easy control by power management register. The LPM3

mode which is Main power domain is off and Always on power domain power on only. When enter standby mode, MS500 power consumption is very low.

The power mode control flow started by CPU settings as figure 7. When power mode set such as LPM1, LPM2, LPM3, then MS500's PMU control isolation and power gating cells to entered pre-defined power mode as Table 7. The wakeup process depends on the which power mode. For example, wakeup from standby mode(LPM3), it needs input from the wake-up pin or chip reset or RTC interrupt.

Figure 7 Power mode operation

As show in the Table 7, MS500 power mode is defined as Active, LPM0, LPM1, LPM2, LPM3. In the Active mode, some power group's power can be controlled by CPU. These power groups are SDMMC host, SDIO slave, SCA, ACA, ARIA.

To wakeup from LPM0, LPM1, LPM2, LPM3, it needs input from outside such as pin interrupt or wakeup pin (PA1).

In the LPM3 mode, PMU operate main power domain off, so wakeup from LPM3 start from ROM boot.

Copyright - © 2019 eWBM Co., Ltd. All rights reserved

#### Table 7 Low Power mode and power domain table

| Power<br>Source              | Power group<br>/Power mode                                                                                                                       | Active                     | LPM0                       | LPM1 | LPM2 | LPM3 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|------|------|------|

|                              | Core Retention F/F                                                                                                                               | On                         | On                         | On   | On   | Off  |

|                              | Core Combination<br>Logic                                                                                                                        | Off                        | On(clock off)              | Off  | Off  | Off  |

|                              | Outside of Core(WIC)                                                                                                                             | On                         | On                         | On   | On   | Off  |

|                              | CRM                                                                                                                                              | On                         | On                         | On   | On   | Off  |

|                              | IO Mux                                                                                                                                           | On                         | On                         | On   | On   | Off  |

|                              | SYSCON, WDT<br>CACHE<br>QSPI<br>e-Fuse, NVM I/F                                                                                                  | On                         | On                         | On   | On   | Off  |

| Main<br>LDO<br>Power         | (Arch. Group)<br>BUSMATRIX<br>DMA<br>UART1, UART2<br>SPI1, SPI2<br>SPI3, SPI4<br>Timer1, Timer2<br>I2C1, I2C2, I2C3, I2C4<br>GPI01, GPI02, GPI03 | On                         | On                         | On   | Off  | Off  |

|                              | ROM                                                                                                                                              | On                         | On                         | On   | On   | Off  |

|                              | SRAM                                                                                                                                             | On                         | On                         | On   | On   | Off  |

|                              | SDMMC Host                                                                                                                                       | On<br>(CPU can set On/Off) | On<br>(CPU can set On/Off) | Off  | Off  | Off  |

|                              | SDIO Slave                                                                                                                                       | On<br>(CPU can set On/Off) | On<br>(CPU can set On/Off) | Off  | Off  | Off  |

|                              | SCA                                                                                                                                              | On<br>(CPU can set On/Off) | On<br>(CPU can set On/Off) | Off  | Off  | Off  |

|                              | ACA                                                                                                                                              | On<br>(CPU can set On/Off) | On<br>(CPU can set On/Off) | Off  | Off  | Off  |

|                              | ARIA                                                                                                                                             | On<br>(CPU can set On/Off) | On<br>(CPU can set On/Off) | Off  | Off  | Off  |

| Always<br>On<br>LDO<br>Power | RTC<br>PMU, Backup-SRAM                                                                                                                          | On                         | On                         | On   | On   | On   |

#### Table 8 Entrance of Low Power Mode Condition

| Low Power Mode     | Condition                                                                 | Entrance Source           |

|--------------------|---------------------------------------------------------------------------|---------------------------|

| LPM0 (without PMU) | CPUWFI or with SLEEPDEEP                                                  | CPU SLEEPING or SLEEPDEEP |

| LPM1(with PMU)     | CPUWFI with SLEEPDEEP<br>HWREG(NVIC SYS CTRL)  = NVIC SYS CTRL SLEEPDEEP; |                           |

| LPM2(with PMU)     | CPUwfi();                                                                 | CPU SLEEPDEEP             |

| LPM3(with PMU)     | HWREG(NVIC_SYS_CTRL) &=<br>~(NVIC_SYS_CTRL_SLEEPDEEP);                    |                           |

#### Table 9 Wakeup Condition of Low Power Mode

| Low Power Mode     | Condition                        | Wakeup Source                                  |

|--------------------|----------------------------------|------------------------------------------------|

| LPM0 (without PMU) | wakeup by CPU wait-for-interrupt | All Interrupts                                 |

| LPM1 (with PMU)    |                                  | SYSCON wakeup signal                           |

| LPM2 (with PMU)    | wakeup by SYSCON Wakeup signals  | (RTC/WAKEUP/RESETN)<br>*RESETN : not recommand |

| LPM3 (with PMU)    | wakeup by AON_PMU                | RTC/PA0/RESETN                                 |

## Table 10 Power Management Register Description

| Offset | Symbol          | Size | Bit   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset<br>Value | Туре |

|--------|-----------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| 0x00   | LPM_STT         | 32   | 31:0  | This register show the current Low Power Status                                                                                                                                                                                                                                                                                                                                                                                                                      |                | R    |

|        | volt_domain_stt | 9    | 8:0   | Power On/Off status of Voltage Domains<br>0- Power Down state 1- Power Up state<br>bit[0] : CPU Retention F/F Power, Outside of Core(WIC, etc)<br>bit[1] : CPU's Core internal Power<br>bit[2] : System Operation Group Power(CRM, SYSCON, WDT,<br>CACHE, QSPI)<br>bit[3] : Peripherals IP Group Power<br>bit[4] : SD/MMC Group Power<br>bit[5] : SDIO Group power<br>bit[6] : Cryptographer Group Power<br>bit[7] : PKA Group Power<br>bit[8] : ARIA Group Power    | -              |      |

|        |                 | 3    | 11:9  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |      |

|        | lpm_stt         | 3    | 14:12 | Low Power Mode Status<br>000 : Normal Operation<br>001 : Low Power mode 1<br>010 : Low Power mode 2<br>011 : Low Power mode 3( Standby Mode)<br>reverved : Normal Operation                                                                                                                                                                                                                                                                                          | -              |      |

|        | -               | 17   | 31:15 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |      |

| 0x04   | LPM_CONF        | 32   | 31:0  | This register is enable the Low Power Mode.<br>When the write command must be run at a time. and then<br>must follow immediately the command of Cortex CPU<br>WIC(Wait for Interrupt Command).<br>For Example with controlling Flash Device's PowerDown and<br>LPM3<br>First, write 0x0001_B000 to LPM_CONF's Register and<br>write wait for interrupt command to CPU.<br>If you want to control without Flash Device Power, write<br>0x0000_B0000 to this register. |                | R/W  |

|      |                   |          |       | Power On/Off setting of Voltage Domains, when                   |      |    |

|------|-------------------|----------|-------|-----------------------------------------------------------------|------|----|

|      |                   |          |       | volt_domain_en is set and Ipm_conf is all zero.                 |      |    |

|      |                   |          |       |                                                                 |      |    |

|      |                   |          |       | 0- Power Off 1- Power On                                        |      |    |

|      |                   |          |       | bit[3:0] : set to 1 (default)                                   |      |    |

|      |                   |          |       | bit[4] : On/Off of SD/MMC Group Power                           |      |    |

|      |                   |          |       | bit[5] : On/Off of SDIO Group power                             |      |    |

|      |                   |          |       | bit[6] : On/Off of Cryptographer Group Power                    |      |    |

|      | volt_domain_conf  | 9        | 8:0   | bit[7] : On/Off of PKA Group Power                              | 1FFh |    |

|      |                   |          |       | bit[8] : On/Off of ARIA Group Power                             |      |    |

|      |                   |          |       |                                                                 |      |    |

|      |                   |          |       | when lpm_conf is not zero, this configure is ignored. According |      |    |

|      |                   |          |       | to lpm_conf, volt_comain_conf is controlled by Hardware as      |      |    |

|      |                   |          |       | below.                                                          |      |    |

|      |                   |          |       | LPM1 : bit[8:0]=9'b0_0000_1101                                  |      |    |

|      |                   |          |       | LPM2 : bit[8:0]=9'b0_0000_0101                                  |      |    |

|      |                   | 2        | 11.0  | LPM3 : bit[8:0]=9'b0_0000_0000                                  |      |    |

|      |                   | 3        | 11:9  | Reserved                                                        |      |    |

|      |                   |          |       | Low Power Mode configuration<br>00 : Normal Operation           |      |    |

|      | Inm conf          | 2        | 13:12 | 01 : Low Power mode 1                                           | 0h   |    |

|      | lpm_conf          | 2        | 13:12 | 10 : Low Power mode 1                                           | UII  |    |

|      |                   |          |       | 11 : Low Power mode 3( Standby Mode)                            |      |    |

|      |                   | 1        | 14    | Reserved                                                        |      |    |

|      |                   | 1        | 17    | Voltage Domain Power On/Off enable on normal operation          |      |    |

|      |                   |          |       | 0 : power control disable 1: power control enable               |      |    |

|      |                   |          |       |                                                                 |      |    |

|      | volt_domain_en    | 1        | 15    | NOTE. This Register is start indicator. This set value does not | 0h   |    |

|      |                   |          |       | auto-refresh.                                                   | •    |    |

|      |                   |          |       | It should be write disable first, if CPU send command again to  |      |    |

|      |                   |          |       | Low Power Mode.                                                 |      |    |

|      |                   |          |       | Flash Device Power Down/On handshake enable Register            |      |    |

|      |                   |          |       | 0: handshake disable 1: handshake enable                        |      |    |

|      | peri_handshake_en | 1        | 16    |                                                                 | 0h   |    |

|      |                   |          |       | NOTE1. If SPI-Flash Boot Mode is set, this must be always       |      |    |

|      |                   |          |       | disable.                                                        |      |    |

|      |                   | 7        | 23:17 | Reserved                                                        |      |    |

|      |                   |          |       | Memory Retention Control by itself (Active Low)                 |      |    |

|      |                   |          |       | 0 - Normal, 1- Retention mode (internal clock off)              |      |    |

|      | mem_ret[2:0]      | 3        | 26:24 | bit[0] : always set to 0                                        | 0h   |    |

|      |                   |          |       | bit[1] : RAM retention                                          |      |    |

|      |                   |          |       | bit[2] : CACHE RAM Retention                                    |      |    |

|      |                   | 1        | 27    | Reserved                                                        |      |    |

|      |                   |          |       | Memory Power Gate enable by itself (Active High)                |      |    |

|      |                   |          |       | 0-Normal, 1- Power-Down                                         |      |    |

|      | mem_pg_en[2:0]    | 3        | 30:28 | bit[0] : ROM Power Down enable (SPI flash direct boot)          | 0h   |    |

|      |                   |          |       | bit[1] : RAM Power Down enable                                  |      |    |

|      |                   | <u> </u> |       | bit[2] : CACHE RAM Power Down enable                            |      |    |

|      | -                 | 1        | 31    | Reserved                                                        | ļ    |    |

| 0x08 | LPM_WAKEUP_CNT    | 32       | 31:0  | This register is the value of power up switching delay.         | -    | RW |

|      |                   |          |       | when escape from Low Power Mode, Switching Delay time           |      |    |

|      | lpm_wakeup_cnt    | 13       | 12:0  | value.                                                          | 0h   |    |

|      | · _ · · ·         | _        | -     | switch delay time = lpm_conf x SYS_CLK(referenced max           |      |    |

|      |                   | 10       | 24.45 | frequency is 12MHz=83ns)                                        |      |    |

| 0.00 | -<br>Decominant   | 19       | 31:13 | Reserved                                                        |      |    |

| 0x0C | Reserved          | 31       | 31:0  | Deserved                                                        | -    |    |

|      | -                 | 31       | 31:8  | Reserved                                                        |      |    |

## **CLOCKS**

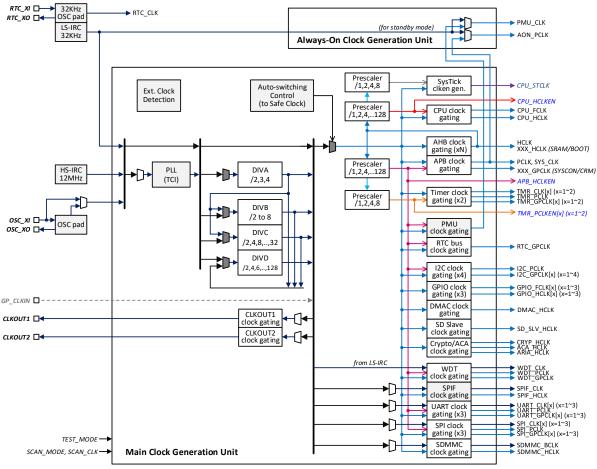

#### **1. CLOCK GENERATION UNIT**

The MS500 clock generation unit is responsible for providing the clock signals to all subsystems and ensuring clean, glitch free switching between the various clock sources.

The MS500 supports many clock sources which can be any one of the following:

- External crystal

- High-speed internal RC oscillator (12MHz)

- Low-speed internal RC oscillator (32KHz)

- A phase-locked loop (PLL),

The clock generation unit also features safe Auto-switching control (to safe clock) and a separate Always-On (AON) Clock Generation Unit for standby mode.

Figure 8 MS500 Clock Generation

Copyright - C 2019 eWBM Co., Ltd. All rights reserved

## 2. CRYSTAL

#### 32 KHz Crystal Oscillator

The RTC oscillator is specifically designed for real time clock (RTC) applications, generates an on-chip asynchronous clock signal using a 32.786 kHz external crystal. It is characterized with crystal loading capacitors ranging from 4 pF to 25 pF.

#### 50 MHz Low Power Crystal Oscillator

The design has been optimized for stability and minimum jitter and can be used over a frequency range of <1MHz to 50MHz.

This oscillator is designed to generate an asynchronous on-chip clock signal with an appropriate external crystal. The design has been optimized for stability and minimum jitter and can be used over a frequency range of <1MHz to 50MHz. Designed to operate on core power only, this low power oscillator has a fixed drive strength with a maximum figure of effort of EF = 0.7 to guarantee stable oscillation.

$$EF = f * C^{0.8} * R^{0.61}$$

Where

EF = figure of effort f = frequency of oscillation C = capacitive loading on XI and XO R = crystal equivalent series resistance

## 3. INTERNAL HIGH-SPEED CLOCK SOURCE

The High-speed(HS) IRC is the high speed clock source of internal clock in the MS500.

The High-speed(HS) IRC is the clock source for the internal high speed clock of the MS500. If the user decides to use this HS-IRC it can be trimmed during testing to achieve the specified accuracy (10%) over the entire voltage and temperature range. Trim values are permanently stored in the internal eFuse area. Additional trim settings can also be stored in flash and can be used to compensate for the changes in operating conditions. The HS IRC default frequency is 12 MHz and it can be select 6MHz or 12MHz by register set.

#### 4. INTERNAL LOW-SPEED CLOCK SOURCE

The Low-speed(LS) IRC is a very low power oscillator, nominally 32KHz, which is primarily used to generate the clocks for the internal peripheral blocks when operating in standby mode or Always-On mode. This does not use RTC clock, RTC clock should come from RTC X'tal (32.768KHz).

#### 5. PLL

The PLL accepts an input clock frequency from an external oscillator or internal IRC.

| <ul> <li>Divided reference frequency range</li> </ul>          | 4.69MHz - 600MHz                 |

|----------------------------------------------------------------|----------------------------------|

| <ul> <li>1 output frequency range</li> </ul>                   | 120MHz - 600MHz                  |

| (VCO output internally divided by 2 for 50% DC)                |                                  |

| – Fout = Fref * NF / NR / OD                                   |                                  |

| <ul> <li>Reference divider values (NF)</li> </ul>              | 1~16                             |

| <ul> <li>Feedback divider values(NR)</li> </ul>                | 1~64                             |

| <ul> <li>Output divider values(OD)</li> </ul>                  | 1~16                             |

| <ul> <li>Output duty cycle (nom, tol)</li> </ul>               | 50%, +/-2%                       |

| <ul> <li>Static phase error (max)</li> </ul>                   | +/-1.25% div. reference cycle    |

| <ul> <li>Period jitter (P-P) (max)</li> </ul>                  | +/-3% output cycle               |

| <ul> <li>Input-to-output jitter (P-P) (max)</li> </ul>         | +/-1.5% div. reference cycle     |

| (jitter numbers are worst-case estimates with supply and subst | rate noise levels below - actual |

| results will be better)                                        |                                  |

| <ul> <li>Power dissipation (nom)</li> </ul>                    | 1.5mA @ 300MHz (/1 output)       |

| <ul> <li>Reset pulse width (min)</li> </ul>                    | 5µs                              |

| <ul> <li>Reset /1 output frequency range</li> </ul>            | 10MHz - 100MHz                   |

| <ul> <li>Lock time (min allowed)</li> </ul>                    | 500 div. reference cycles        |

| (actual lock time will be much smaller)                        |                                  |

| <ul> <li>Freq. overshoot (full-~/half-~) (max)</li> </ul>      | 40%/50%                          |

Copyright - © 2019 eWBM Co., Ltd. All rights reserved

#### 6. ALWAYS-ON CLOCK GENERATION UNIT

The external VDD\_AON (Always-On power supply) supplies the power to the power domain and the LDO\_M\_DVDD (Main power supply) provide the main power domain.

When the main power domain is off, the always-on domain will remain alive with a low frequency clock such as the internal low speed cock.

To wake up from standby mode, a wake up signal must be provided to the WAKEUP pin (Active High) or RESETN pin (Active Low).

## RESET

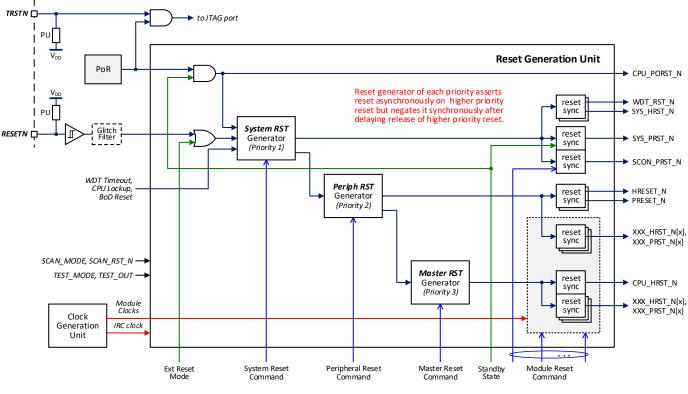

A power on reset is required to place the device in a known good state after power-up. The MS500 is reset by internal Power-on Reset (PoR) module, the external reset signal, or the Watchdog Timer. In all cases, the MS500 restart program execution from the address provided by the reset entry point. A register can be later referenced to determine the source of the reset. The reset signal also propagates to the CPU peripherals and the rest of the CPU subsystems.

## **1. RESET GENERATION DIAGRAM**

**Figure 9 Reset Generation Block Diagram**

#### 2. RESET SOURCES

Power on Reset (PoR)

Power-on reset is initiated by the PoR (power on reset module) inside of MS500. Power on reset sets all of the device internal logic to its default state. This PoR operates followed by power on stage as automatically.

External Reset Input Pin (RESETN) assertion

The external reset pin (RESETN) is resets the MS500 including the core and all the on-chip peripherals except JTAG.

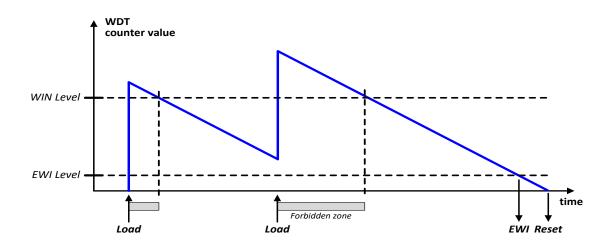

A Watchdog Timer

Watchdog timer consists of a 32-bit down counter with a programmable timeout interval that has the capability to generate an interrupt and a reset signal on timing out. It is used to apply a reset to a system in the event of a software failure.

#### 3. RESET GENERATION STRUCTURE

| Reset               |     |             |     | Target |      |     |            |                                      |  |

|---------------------|-----|-------------|-----|--------|------|-----|------------|--------------------------------------|--|

| Hierarchy           | CRM | SysCon, PMU | WDT | Bus    | Peri | CPU | AON Domain | Reset Source                         |  |

| Power<br>Reset      | Yes | Yes         | Yes | Yes    | Yes  | Yes | Yes        | V <sub>DD</sub> Power on Reset (PoR) |  |

|                     |     |             |     |        |      |     |            | Higher Priority (0) Reset            |  |

|                     |     |             |     |        |      | Yes | -          | External reset pin                   |  |

| System              | Yes | Yes         | Yes | Yes    | Yes  |     |            | Watchdog Timeout Reset, CPU Lockup   |  |

| Reset               |     |             |     |        |      |     |            | Detection, BoD Reset                 |  |

|                     |     |             |     |        |      |     |            | Reset Command                        |  |

|                     |     |             |     |        |      |     |            | (Group or Module)                    |  |

|                     |     |             |     |        |      |     |            | Higher Priority (1) Reset            |  |

| Peripheral<br>Reset | -   | -           | -   | Yes    | Yes  | Yes | -          | Reset Command                        |  |

| neset               |     |             |     |        |      |     |            | (Group or Module)                    |  |

| Wakeup              | Yes | Voc         | Yes | Voc    | Voc  | Voc |            | Wakeup from Standby mode             |  |

| reset               | 162 | Yes         | 162 | Yes    | Yes  | Yes |            | (Wake-up pin)                        |  |

Table 11 MS500 Reset Hierarchy

- CRM : Clock reset module

- PMU : Power Management Unit

- WDT : Watchdog

- AON Domain : Always on Power domain

### 4. RESET GENERATION SIGNAL

#### Table 12 RESET GENERATION SIGNAL

| Module                 | Hierarchy                | Clock Name    | Brief Description                                                                                           | Reset Source                              | Sync Clock<br>(@Release) | SW<br>Command |

|------------------------|--------------------------|---------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------|---------------|

| CPU                    | Power Reset              | CPU_PORSTN    | Cortex-M0 power reset<br>Cortex-M0 includes reset sync logic<br>for power reset.                            | PoR (V <sub>DD</sub> )                    | -                        | -             |