# 256Kx8 LOW VOLTAGE, SERIAL SRAM with SPI, SDI and SQI INTERFACE

**JULY 2021**

#### **KEY FEATURES**

- · SPI-Compatible Bus Interface:

- 16/20 MHz Clock rate

- SPI/SDI/SQI mode

- · Low-Power CMOS Technology:

- Read Current: 8 mA (max) at 3.6V, 20 MHz, 85°C.

- CMOS Standby Current: 4 uA (typ).

- 256K x 8-bit Organization:

- 32-byte page

- Byte, Page and Sequential mode for Reads and Writes

- Temperature Ranges Supported:

- Industrial (I): -40°C to +85°C

Automotive (A3): -40°C to +125°C

- · RoHS Compliant

- 8-pin SOIC package

#### **DESCRIPTION**

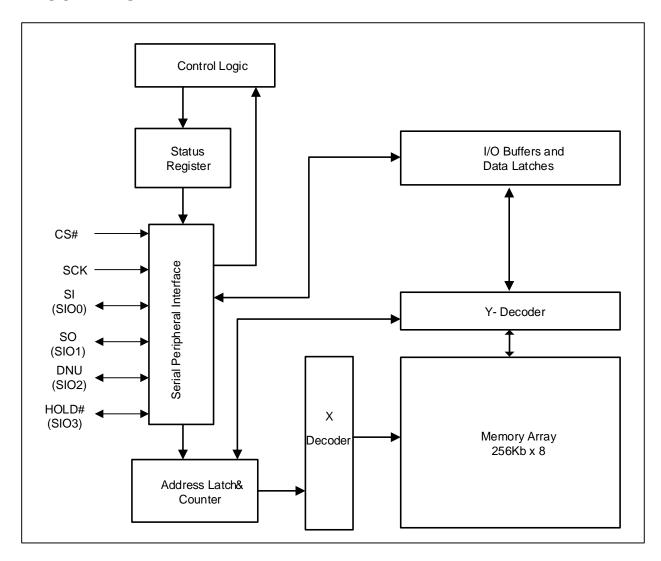

The ISSI IS62/65WVS2568FALLFBLL are 2M bit Serial static RAMs organized as 256K bytes by 8 bits. It is fabricated using ISSI's high-performance CMOS technology.

The device is accessed via a simple Serial Peripheral Interface (SPI) compatible serial bus. The bus signals required are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access the device is controlled through a Chip Select (CS#) input. Additionally, SDI (Serial Dual Interface) and SQI (Serial Quad Interface) is supported if your application needs faster data rates.

This device also supports unlimited reads and writes to the memory array.

The IS62/65WVS5128FALL/FBLL are available in the standard 8-pin SOIC package.

Copyright © 2021 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

# **BLOCK DIAGRAM**

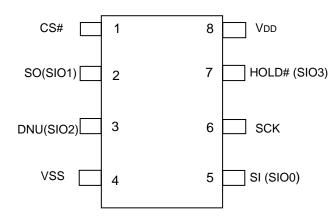

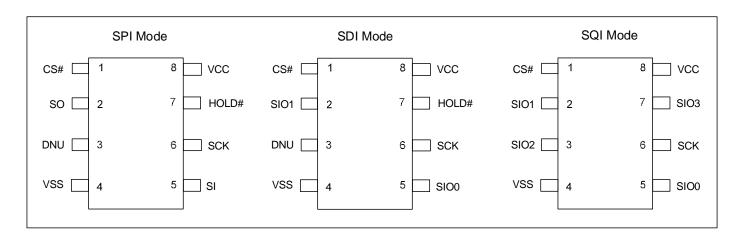

# **PIN CONFIGURATIONS**

8-pin SOIC

## **PIN DESCRIPTIONS**

| CS#        | Chip Enable Input  |

|------------|--------------------|

| SO/SIO1    | Serial Output/SIO1 |

| DNU/SIO2   | Do Not Use/SIO2    |

| VSS        | Ground             |

| SI/SIO0    | Serial Input/SIO0  |

| SCK        | Serial Clock       |

| HOLD#/SIO3 | HOLD#/SIO3         |

| VDD        | Power              |

|            |                    |

# IS62/65WVS2568FALL IS62/65WVS2568FBLL

## Chip Select (CS#)

A low level on this pin selects the device. A high level deselects the device and forces it into Standby mode. When the device is deselected, SO goes to the high- impedance state, allowing multiple parts to share the same SPI bus. After power-up, a low level on CS# is required, prior to any sequence being initiated.

### Serial Clock (SCK)

The SCK is used to synchronize the communication between a master and Serial SRAM. Instructions, addresses or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin is updated after the falling edge of the clock input.

#### Serial Output (SO: SPI mode)

The SO pin is used to transfer data out of the device. During a read cycle, data is shifted out on this pin after the falling edge of the serial clock.

## Serial Input (SI: SPI mode)

The SI pin is used to transfer data into the device. It receives instructions, addresses, and data. Data is latched on the rising edge of the serial clock.

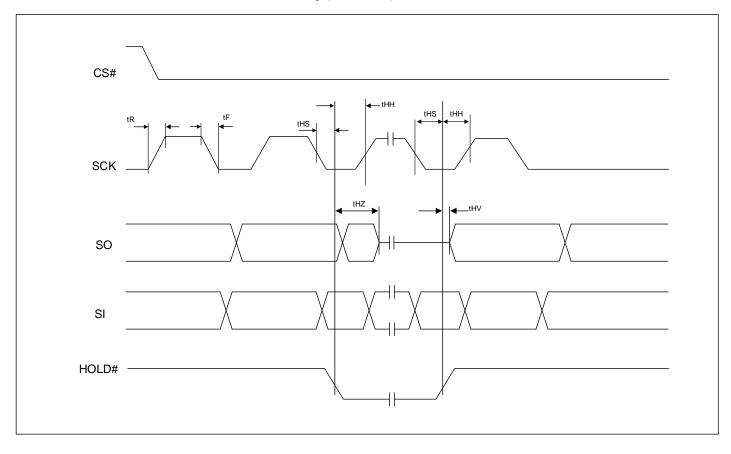

#### **HOLD Function (HOLD#: SPI Mode, and SDI Mode)**

The HOLD# pin is used to suspend transmission to Serial SRAM while in the middle of a serial sequence without having to re-transmit the entire sequence over again. It must be held high any time this function is not being used. Once the device is selected and a serial sequence is underway, the HOLD# pin may be pulled low to pause further serial communication without resetting the serial sequence.

The HOLD# pin should be brought low while SCK is low, otherwise the HOLD function will not be invoked until the next SCK high-to-low transition. The device must remain selected during this sequence. The SI and SCK levels are "don't cares" during the time the device is paused and any transitions on these pins will be ignored. To resume serial communication, HOLD# should be brought high while the SCK pin is low, otherwise serial communication will not be resumed until the next SCK high-to-low transition.

The SO line will tri-state immediately upon a high-to low transition of the HOLD# pin, and will begin outputting again Immediately upon a subsequent low- to-high transition of the HOLD pin, independent of the state of SCK.

Hold functionality is not available when operating in Quad SPI mode

#### Serial Input / Output Pins (SIO0, SIO1: SDI Mode)

The SIO0 and SIO1 pins are used for Dual SPI mode of operation (SI→SIO0, SO-->SIO1). Functionality of these I/O pins is shared with SO and SI.

## Serial Input / Output Pins (SIO0, SIO1, SIO2, SIO3: SQI Mode)

The SIO0 through SIO3 pins are used for Quad SPI mode of operation. Because of the shared functionality of these pins the HOLD# feature is not available when using Quad SPI mode (Hold# →SIO3 in Quad SPI mode)

#### DNU/SIO2 (Do Not Use or SIO2)

Pin 3 is DNU (Do No Use) in SPI mode and SDI mode. SIO2 in SQI mode.

# IS62/65WVS2568FALL IS62/65WVS2568FBLL

### **FUNCTION DESCRIPTION**

Serial SRAM is designed to interface directly with the Serial Peripheral Interface (SPI). It can also interface with Multi-IO SPI interface (Dual SPI and Quad SPI).

The device contains an 8-bit instruction register. The device is accessed via the SI pin, with data\_being clocked in on the rising edge of SCK. The CS# pin must be low for the entire operation.

All instructions, addresses and data are transferred MSB first, LSB last.

#### **OPERATION MODE**

The device has three modes of operation that are selected by setting bits 7 and 6 in the MODE register. The modes of operation are Byte, Page and Sequential.

## **Byte Operation**

Byte Operation is selected when bits 7 and 6 in the MODE register are set to 00. In this mode, the read/ write operations are limited to only one byte. The Command followed by the 24-bit address is clocked into the device and the data to/from the device is transferred on the next eight clocks.

### **Page Operation**

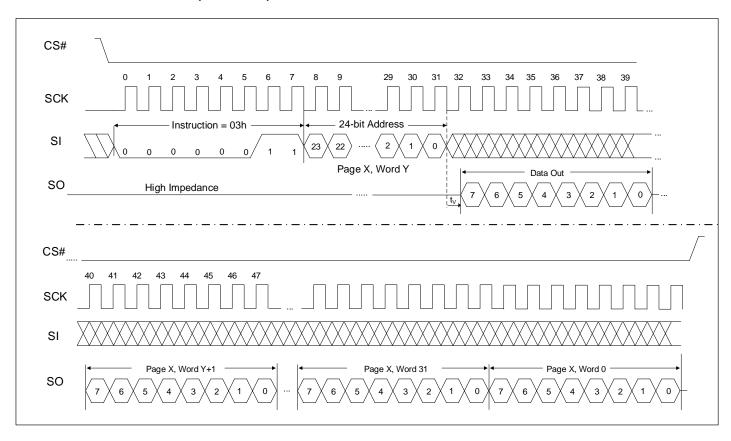

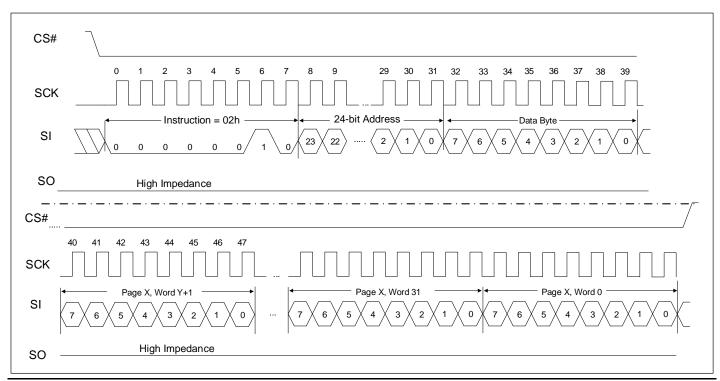

Page Operation is selected when bits 7 and 6 in the MODE register are set to 10. The device has 8192 pages of 32 bytes. In this mode, the read and write operations are limited to within the addressed page (the address is automatically incremented internally). If the data being read or written reaches the page boundary, then the internal address counter will increment to the start of the page.

#### **Sequential Operation**

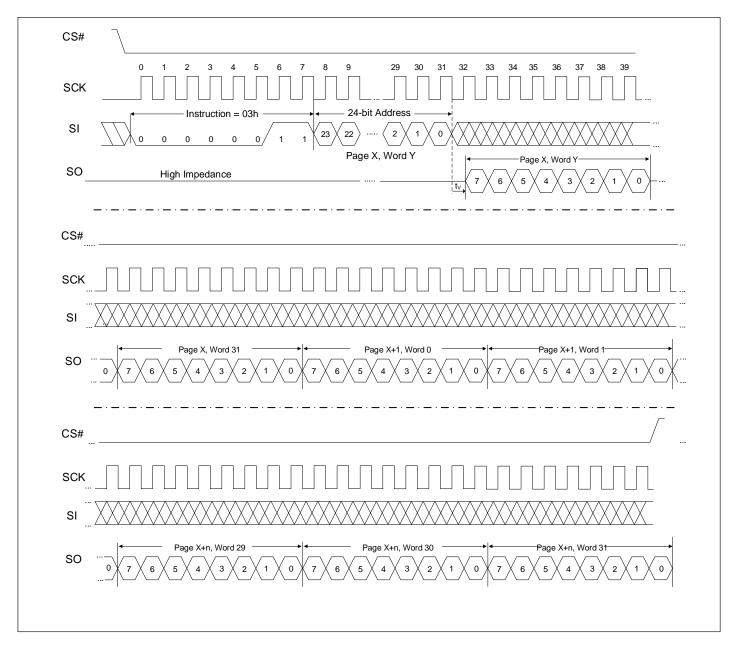

Sequential Operation is selected when bits 7 and 6 in the MODE register are set to 01. Sequential operation allows the entire array to be written to and read from. The internal address counter is automatically incremented and page boundaries are ignored. When the internal address counter reaches the end of the array, the address counter will roll over to 0x00000.

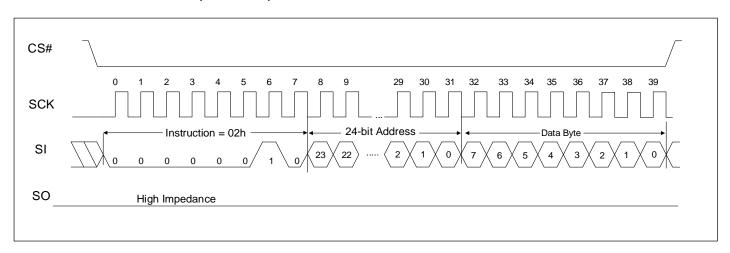

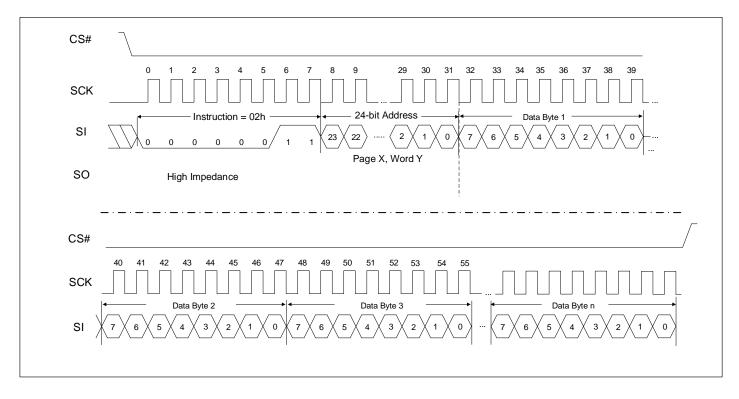

#### **WRITE MODE**

Prior to any attempt to write data to the device, the device must be selected by bringing CS# low. Once the device is selected, the Write command can be started by issuing a WRITE instruction, followed by the 24-bit address, with the first six MSB's of the address being a "don't care" bit, and then the data to be written. A write is terminated by the CS# being brought high.

If operating in Page mode, after the initial data byte is shifted in, additional bytes can be shifted into the device. The Address Pointer is automatically incremented. This operation can continue for the entire page (32 bytes) before data will start to be overwritten.

If operating in Sequential mode, after the initial data byte is shifted in, additional bytes can be clocked into the Device. The internal Address Pointer is automatically incremented. When the Address Pointer reaches the highest Address (3FFFh), the address counter rolls over to (00000h). This allows the operation to continue indefinitely. However previous data will be overwritten.

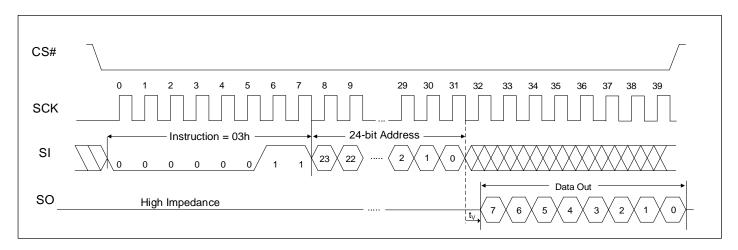

#### **READ MODE**

The device is selected by pulling CS# Low. Then 8 bit instruction is transmitted to the device followed by the 24 bit address, with the first six MSB's of the address being a "don't care" bit.

After the correct READ instruction and address are sent, the data stored in the memory at the selected address is shifted out on the SO pin. If operating in Sequential mode, the data stored in the memory at the next address can be read sequentially by continuing to provide clock pulses.

The internal Address Pointer is automatically incremented to the next higher address after each byte of data is shifted out. When the highest address is reached (3FFFFh), the address counter rolls over to address 00000h, allowing the read cycle to be continued indefinitely. The read operation is terminated by raising the CS# pin.

## **INSTRUCTION SET**

| Instruction Name | Instruction Format | Hex<br>Code | Description                                               |

|------------------|--------------------|-------------|-----------------------------------------------------------|

| READ             | 0000 0011          | 0x03        | Read data from memory array beginning at selected address |

| WRITE            | 0000 0010          | 0x02        | Write data to memory array beginning at selected address  |

| ESDI             | 0011 1011          | 0x3B        | Enter SDI mode                                            |

| ESQI             | 0011 1000          | 0x38        | Enter SQI mode                                            |

| RSTDQI           | 1111 1111          | 0xFF        | Reset SDI/SQI mode                                        |

| RDMR             | 0000 0101          | 0x05        | Read Mode Register                                        |

| WRMR             | 0000 0001          | 0x01        | Write Mode Register                                       |

## **BYTE READ OPERATION (SPI MODE)**

# **BYTE WRITE OPERATION (SPI MODE)**

## PAGE READ OPERATION (SPI MODE)

# **PAGE WRITE OPERATION (SPI MODE)**

# **SEQUENTIAL READ OPERATION (SPI MODE)**

## **SEQUENTIAL WRITE OPERATION (SPI MODE)**

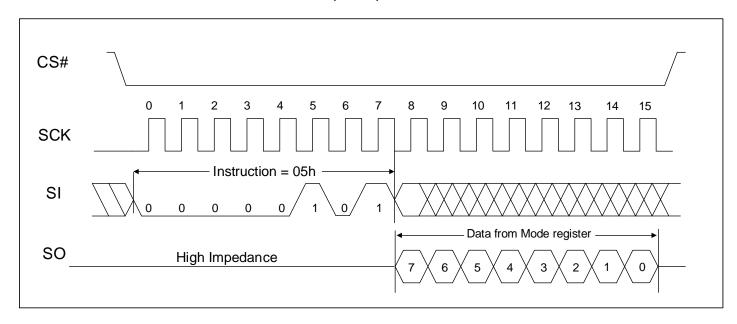

## **READ MODE REGISTER INSTRUCTION (RDMR)**

The Read Mode Register instruction (RDMR: 05h) provides access to the MODE register. The MODE register may be read at any time. The MODE register is formatted as follows:

| •                       |   |          |   |   |   |   |   |

|-------------------------|---|----------|---|---|---|---|---|

| 7                       | 6 | 5        | 4 | 3 | 2 | 1 | 0 |

| W/R                     |   | _        | _ | _ | _ | _ | _ |

| MODE                    |   | Reserved |   |   |   |   |   |

| W/R = writable/readable |   |          |   |   |   |   |   |

The mode bits (7:6) indicate the operating mode of the SRAM. The possible modes of operation are:

- 0 0= Byte mode

- 1 0= Page mode

- 0 1= Sequential mode (default operation)

- 1 1= Reserved

Bits 0 through 5 are reserved and should always be set to '0'.

## READ MODE REGISTER OPERATION TIMING (RDMR)

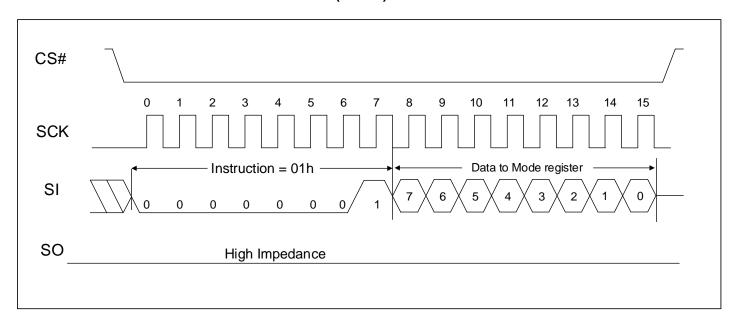

### WRITE MODE REGISTER INSTRUCTION (WRMR)

The Write Mode Register instruction (WRMR: 01h) allows the user to write to the bits in the MODE register.

This allows for setting of the Device operating mode. Several of the bits in the MODE register must be cleared to '0'.

## WRITE MODE REGISTER OPERATION TIMING (WRMR)

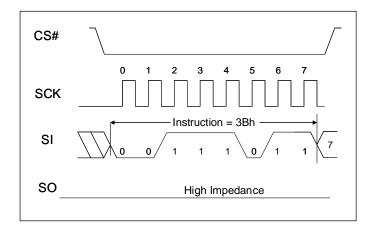

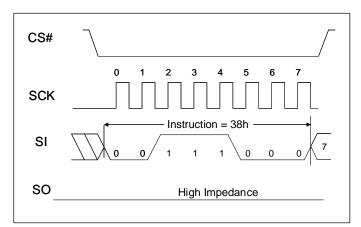

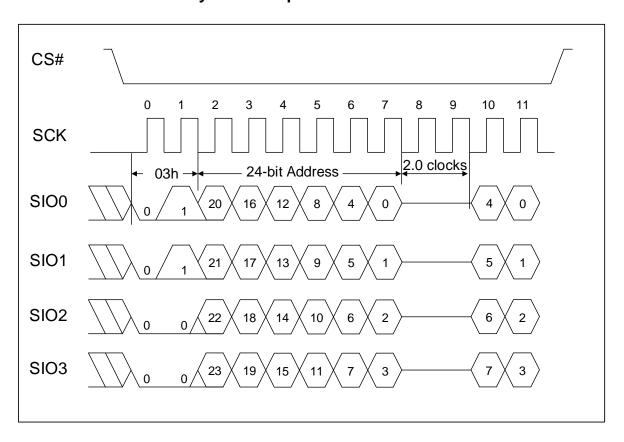

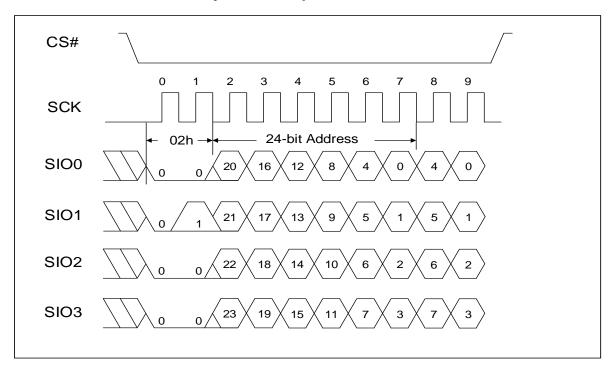

#### SDI MODE AND SQI MODE OPERATION

The device also supports SDI (Serial Dual Interface) and SQI (Serial Quad Interface) mode of operation when used with compatible master devices. To enter SDI mode, the ESDI command (3Bh) must be clocked in. As a convention for SDI mode of operation, two bits are entered per clock using the SIO0 and SIO1 pins. Bits are clocked MSB first.

To enter SQI mode, the ESQI command (38h) must be clocked in. For SQI mode of operation, four bits of data are entered per clock, or one nibble per clock. The nibbles are clocked MSB first.

## **Enter SDI Mode**

#### **Enter SQI Mode**

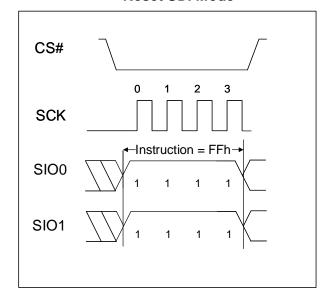

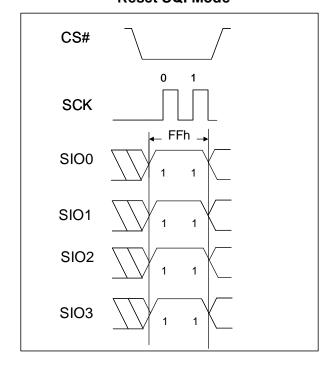

To exit from SDI mode, the RSTDQI command (FFh) must be issued. The command must be entered in the current device configuration, either SDI mode or SQI mode.

## **Reset SDI Mode**

## **Reset SQI Mode**

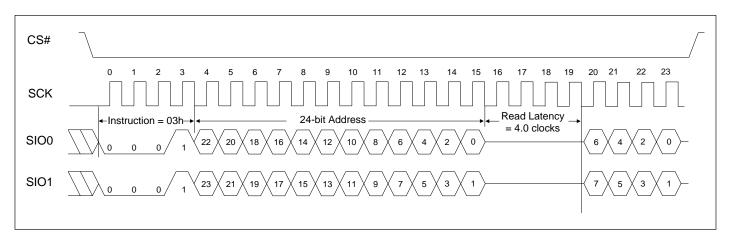

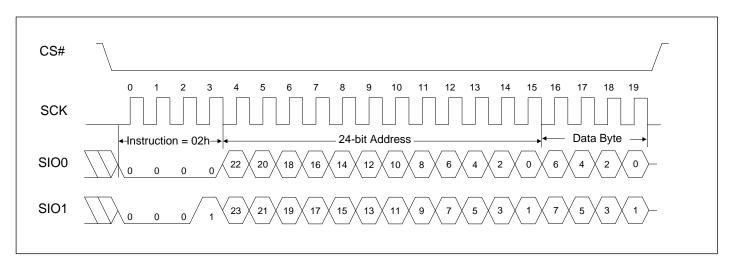

## SDI (SERIAL DUAL INTERFACE) MODE OPERATION

The device supports Serial Dual Interface (SDI) mode of operation. There are 4.0 clock cycles (Dummy Byte) of Read Latency in SDI mode Byte Read Operation. No Write Latency in SDI Write Operation. It should be noted that if the MCU resets before the SRAM, the user will need to determine the serial mode of operation of the SRAM and reset it accordingly.

#### Byte Read Operation in SDI Mode

#### Byte Write Operation in SDI Mode

# Byte Read Operation in SQI Mode

# **Byte Write Operation in SQI Mode**

## ABSOLUTE MAXIMUM RATINGS AND OPERATING RANGE

#### **ABSOLUTE MAXIMUM RATINGS (1)**

| Symbol   | Parameter                            | Value                         | Unit |

|----------|--------------------------------------|-------------------------------|------|

| Vterm    | Terminal Voltage with Respect to GND | $-0.2$ to $+3.9(V_{DD}+0.3V)$ | V    |

| tBIAS    | Temperature Under Bias               | -55 to +125                   | °C   |

| $V_{DD}$ | V <sub>DD</sub> Related to GND       | $-0.2$ to $+3.9(V_{DD}+0.3V)$ | V    |

| tStg     | Storage Temperature                  | -65 to +150                   | °C   |

#### Notes:

#### **OPERATING RANGE** (1)

| Range      | Ambient Temperature | Device Marking  | VDD        |

|------------|---------------------|-----------------|------------|

| Industrial | -40°C to +85°C      | IS62WVS2568FALL | 1.65V-2.2V |

| Industrial | -40°C to +85°C      | IS62WVS2568FBLL | 2.2V-3.6V  |

| Automotive | -40°C to +125°C     | IS65WVS2568FBLL | 2.2V-3.6V  |

#### Note:

#### PIN CAPACITANCE (1)

| Parameter                             | Symbol           | Test Condition                                     | Max | Units |

|---------------------------------------|------------------|----------------------------------------------------|-----|-------|

| Input capacitance ( CS#, SCK)         | Cin              | T 25°C f 1 MHz \/ \/ (t) (5)                       | 6   | pF    |

| Input/Output capacitance (other pins) | C <sub>I/O</sub> | $T_A = 25$ °C, $f = 1$ MHz, $V_{DD} = V_{DD}(typ)$ | 8   | pF    |

#### Note:

Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification

is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> Full device AC operation assumes a 100 µs ramp time from 0 to Vcc(min) and 200 µs wait time after Vcc stabilization.

<sup>1.</sup> These parameters are guaranteed by design and tested by a sample basis only.

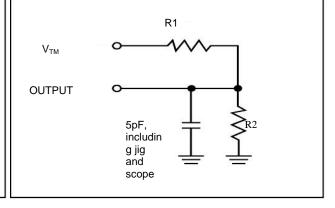

# AC TEST CONDITIONS (OVER THE OPERATING RANGE)

| Parameter                     | Unit<br>(1.65V~2.2V)  | Unit<br>(2.2V~2.7V)     | Unit<br>(2.7V~3.6V)   |  |  |

|-------------------------------|-----------------------|-------------------------|-----------------------|--|--|

| Input Pulse Level             | 0V to V <sub>DD</sub> | 0V to V <sub>DD</sub>   | 0V to V <sub>DD</sub> |  |  |

| Input Rise and Fall Time      | 1V/ns                 | 1V/ns                   | 1V/ns                 |  |  |

| Output Timing Reference Level | 0.9V                  | ½ V <sub>DD</sub>       | ½ V <sub>DD</sub>     |  |  |

| R1                            | 13500                 | 16667                   | 1103                  |  |  |

| R2                            | 10800                 | 15385                   | 1554                  |  |  |

| V <sub>TM</sub>               | 1.8V                  | $V_{DD}$                | $V_{DD}$              |  |  |

| Output Load Conditions        |                       | Refer to Figure 1 and 2 |                       |  |  |

## **OUTPUT LOAD CONDITIONS FIGURES**

\_\_

Pigure1

R1

OUTPUT

30pF, includin g jig and scope

Figure2

## **ELECTRICAL CHARACTERISTICS**

# IS62WVS2568FALL DC ELECTRICAL CHARACTERISTICS-I (OVER THE OPERATING RANGE) VDD=1.65V~2.2V

| Symbol                         | Parameter              | Test Conditions                                              | Min. | Тур. | Max.           | Unit |

|--------------------------------|------------------------|--------------------------------------------------------------|------|------|----------------|------|

| V <sub>OH</sub>                | Output HIGH Voltage    | I <sub>OH</sub> = -0.1 mA                                    | 1.4  | -    | -              | V    |

| Vol                            | Output LOW Voltage     | I <sub>OL</sub> = 0.1 mA                                     | -    | -    | 0.2            | V    |

| V <sub>IH</sub> <sup>(1)</sup> | Input HIGH Voltage     |                                                              | 1.4  | -    | $V_{DD} + 0.2$ | V    |

| $V_{IL}^{(1)}$                 | Input LOW Voltage      |                                                              | -0.2 | -    | 0.4            | V    |

| $V_{DR}^{(2)}$                 | Data Retention Voltage |                                                              | -    | 1.0  | -              | V    |

| ILI                            | Input Leakage          | GND < V <sub>IN</sub> < V <sub>DD</sub>                      | -1   | -    | 1              | μΑ   |

| I <sub>LO</sub>                | Output Leakage         | GND < V <sub>IN</sub> < V <sub>DD</sub> , Output<br>Disabled | -1   | -    | 1              | μA   |

#### Notes

- VILL (min) = -1.0V AC (pulse width < 10ns). Not 100% tested.</li>

VIHH (max) = VDD + 1.0V AC (pulse width < 10ns). Not 100% tested.</li>

- 2. This is the limit to which VDD can be lowered without losing RAM data at TA = 25°C. This parameter is periodically sampled and not 100% tested.

# IS62 (5) WVS2568FBLL DC ELECTRICAL CHARACTERISTICS-I (OVER THE OPERATING RANGE) VDD=2.2V~3.6V

| Symbol                         | Parameter              | Test Conditions                                           | Min.      | Тур. | Max.           | Unit |

|--------------------------------|------------------------|-----------------------------------------------------------|-----------|------|----------------|------|

| Vон                            | Output HIGH Voltage    | $2.2 \le V_{DD} < 2.7$ , $I_{OH} = -0.1$ mA               | 2.0       | -    | -              | V    |

|                                |                        | $2.7 \le V_{DD} \le 3.6$ , $I_{OH} = -1.0 \text{ mA}$     | 2.4       | -    | -              | V    |

| Vol                            | Output LOW Voltage     | $2.2 \le V_{DD} < 2.7$ , $I_{OL} = 0.1$ mA                | -         | -    | 0.4            | V    |

|                                |                        | $2.7 \le V_{DD} \le 3.6$ , $I_{OL} = 2.1$ mA              | -         | -    | 0.4            | V    |

| V <sub>IH</sub> <sup>(1)</sup> | Input HIGH Voltage     | 2.2 ≤ V <sub>DD</sub> < 2.7                               | 1.8       | -    | $V_{DD} + 0.3$ | V    |

|                                |                        | 2.7 ≤ V <sub>DD</sub> ≤ 3.6                               | 2.2       | -    | $V_{DD} + 0.3$ | V    |

| V <sub>IL</sub> <sup>(1)</sup> | Input LOW Voltage      | 2.2 ≤ V <sub>DD</sub> < 2.7                               | -0.3      | -    | 0.6            | V    |

|                                |                        | 2.7 ≤ V <sub>DD</sub> ≤ 3.6                               | -0.3      | -    | 0.8            | V    |

| V <sub>DR</sub> <sup>(2)</sup> | Data Retention Voltage |                                                           | -         | 1.0  | -              | V    |

| ILI                            | Input Leakage          | GND < V <sub>IN</sub> < V <sub>DD</sub>                   | -1        | -    | 1              | μA   |

| ILO                            | Output Leakage         | GND < V <sub>IN</sub> < V <sub>DD</sub> , Output Disabled | <b>–1</b> | -    | 1              | μΑ   |

#### Notes:

- VILL (min) = -2.0V AC (pulse width < 10ns). Not 100% tested.</li>

VIHH (max) = VDD + 2.0V AC (pulse width < 10ns). Not 100% tested.</li>

- 2. This is the limit to which VDD can be lowered without losing RAM data at TA = 25°C. This parameter is periodically sampled and not 100% tested.

# IS62/65WVS2568FALL IS62/65WVS2568FBLL

# IS62WVS2568FALL DC ELECTRICAL CHARACTERISTICS-II FOR POWER (OVER THE OPERATING RANGE)

| Symbol | Parameter                     | Test Conditions                                 | Grade | -1   | -16  |    |

|--------|-------------------------------|-------------------------------------------------|-------|------|------|----|

|        |                               |                                                 |       | Тур. | Max. |    |

| ICC    | V <sub>DD</sub> Dynamic       | $V_{DD} = Max$ , $f = f_{MAX}$ , $CS# = V_{IL}$ | Com.  |      | 7    |    |

|        | Operating Supply Current      | $I_{OUT} = 0 \text{ mA}$                        | Ind.  | -    | 8    | mA |

| ICDO   | CMOS Standby<br>Current (CMOS | $V_{DD} = Max, f = 0, CS\# \ge V_{DD} - 0.2V$   | Com.  | 4    | 10   | ^  |

| ISB2   | Inputs)                       | $VIN \le 0.2V$ or $VIN \ge V_{DD} - 0.2V$       | Ind.  | 4    | 20   | μΑ |

Note:

# IS62 (5) WVS2568FBLL DC ELECTRICAL CHARACTERISTICS-II FOR POWER (OVER THE OPERATING RANGE)

| Symbol | Parameter               | Test Conditions                                                              | Grade | -2   | 20   | -    | 16   | Unit |

|--------|-------------------------|------------------------------------------------------------------------------|-------|------|------|------|------|------|

|        |                         |                                                                              |       | Тур. | Max. | Тур. | Max. |      |

| ICC    | V <sub>DD</sub> Dynamic | $V_{DD} = Max$ , $f = f_{MAX}$ , $CS# = V_{IL}$                              | Com.  |      | 7    |      | 7    |      |

|        | Operating               | $I_{OUT} = 0 \text{ mA}$                                                     | Ind.  | -    | 8    | -    | 8    | mΑ   |

|        | Supply Current          |                                                                              | Auto. |      | 13   |      | 13   |      |

|        | CMOS Standby            | $V_{DD} = Max, f = 0$                                                        | Com.  |      | 10   |      | 10   |      |

| ISB2   | Current (CMOS Inputs)   | $CS\# \ge V_{DD} - 0.2V$<br>$VIN \le 0.2V \text{ or } VIN \ge V_{DD} - 0.2V$ | Ind.  | 4    | 20   | 4    | 20   | μΑ   |

|        |                         | VIIV = 0.2 V OI VIIV = VDD - 0.2 V                                           | Auto. |      | 36   |      | 36   |      |

Note:

<sup>1.</sup> Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at TA = 25°C.

<sup>1.</sup> Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at TA = 25°C.

# AC CHARACTERISTICS (1) (OVER OPERATING RANGE)

# **READ/WRITE CYCLE AC CHARACTERISTICS**

| Parameter                   | Symbol | -2  | 20  | -16 |     | unit | notes |

|-----------------------------|--------|-----|-----|-----|-----|------|-------|

| Parameter                   | Symbol | Min | Max | Min | Max | unit | notes |

| Clock Frequency             | FCLK   | -   | 20  | -   | 16  | MHz  |       |

| CS# Setup Time              | tCSS   | 25  | -   | 32  | -   | ns   |       |

| CS# Hold Time               | tCSH   | 50  | -   | 50  | -   | ns   |       |

| CS# Disable Time            | tCSD   | 25  | -   | 32  | -   | ns   |       |

| Data Setup Time             | tDS    | 10  | -   | 10  | -   | ns   |       |

| Data Hold Time              | tDH    | 10  | -   | 10  | -   | ns   |       |

| Clock High Time             | tCKH   | 23  | -   | 32  | -   | ns   |       |

| Clock Low Time              | tCKL   | 23  | -   | 32  | -   | ns   |       |

| Clock Delay Time            | tCLD   | 25  | -   | 32  | -   | ns   |       |

| Output Valid from Clock Low | tV     | -   | 25  | -   | 36  | ns   |       |

| Output Hold Time            | tOH    | 0   | -   | 0   | -   | ns   | 1     |

| CS# High to Output High-Z   | tCHZ   | -   | 20  | -   | 20  | ns   | 1     |

| HOLD# Setup Time            | tHS    | 10  | -   | 10  | -   | ns   |       |

| HOLD# Hold Time             | tHH    | 10  | -   | 10  | -   | ns   |       |

| HOLD# Low to Output High-Z  | tHZ    | -   | 20  | -   | 20  | ns   | 1     |

| HOLD# High to Output Valid  | tHV    | -   | 50  | -   | 50  | ns   |       |

Note:

1. Not 100% tested.

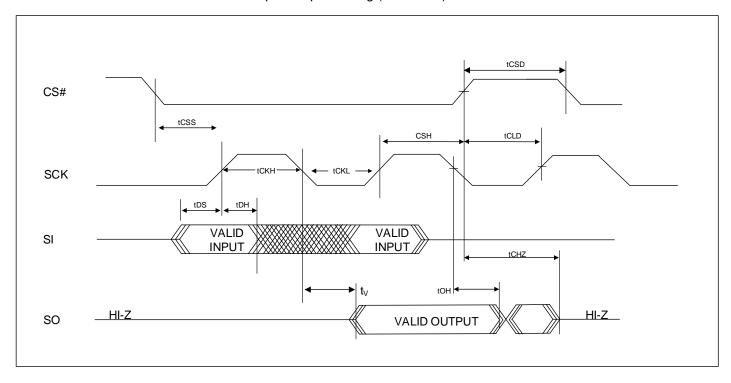

# **TIMING DIAGRAM**

## Serial Input/Output Timing (SPI Mode)

## HOLD Timing (SPI Mode)

## **ORDERING INFORMATION**

# IS62WVS2568FALL (1.65V - 2.2V)

Industrial Range: -40°C to +85°C

| Speed (MHz) | Order Part No.        | Package                      |

|-------------|-----------------------|------------------------------|

| 16          | IS62WVS2568FALL-16NLI | 8-pin SOIC 150mil, Lead-free |

# IS62/65WVS2568FBLL (2.2V - 3.6V)

Industrial Range: -40°C to +85°C

| Speed (MHz) | Order Part No.        | Package                      |

|-------------|-----------------------|------------------------------|

| 20          | IS62WVS2568FBLL-20NLI | 8-pin SOIC 150mil, Lead-free |

| 16          | IS62WVS2568FBLL-16NLI | 8-pin SOIC 150mil, Lead-free |

# Automotive Range (A3): -40°C to +125°C

| Speed (MHz) | Order Part No.         | Package                      |

|-------------|------------------------|------------------------------|

| 16          | IS65WVS2568FBLL-16NLA3 | 8-pin SOIC 150mil, Lead-free |

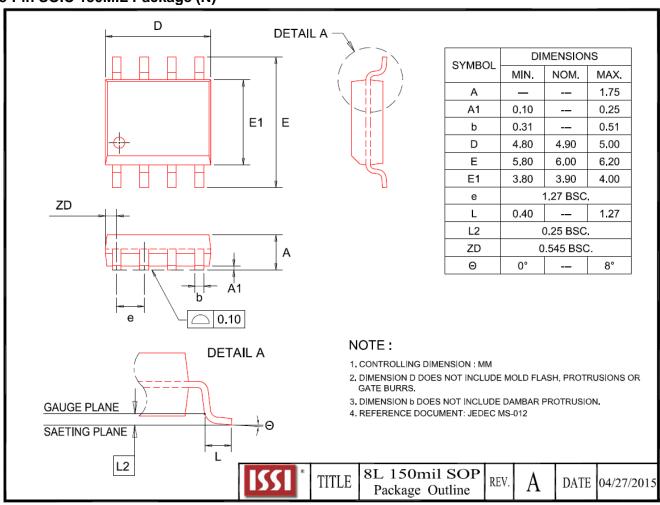

## **PACKAGE INFORMATION**

## 8-Pin SOIC 150MIL Package (N)