# GigaDevice Semiconductor Inc.

## **GD32207I-EVAL Evaluation Board**

## **User Manual**

# **Table of Contents**

| TAE  | BLE OF CONTENTS          | 1  |

|------|--------------------------|----|

| LIS  | ST OF FIGURES            | 5  |

| LIS  | ST OF TABLES             | 7  |

| 1.   | INTRODUCTION             | 8  |

| 2.   | FUNCTION PIN ASSIGNMENT  | 8  |

| 3.   | GETTING STARTED          | 12 |

| 4.   | HARDWARE LAYOUT OVERVIEW | 12 |

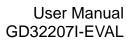

| 4.1. | . Power supply           | 12 |

| 4.2. | Boot option              | 13 |

| 4.3. | . LED                    | 13 |

| 4.4. | . Key                    | 14 |

| 4.5. | . USART1                 | 14 |

| 4.6. | ADC/DAC                  | 15 |

| 4.7. | . I2C                    | 15 |

| 4.8. | SPI-Serial Flash         | 16 |

| 4.9. | . USB                    | 16 |

| 4.10 | 0. CAN                   | 17 |

| 4.11 | 1. RTC                   | 17 |

| 4.12 | 2. TLDI RGB-LCD          | 18 |

| 4.13 | 3. EXMC-NAND Flash       | 18 |

| 4.14 | 4. Ethernet              | 19 |

| 4.15.  | GD-Link                       | 19 |

|--------|-------------------------------|----|

| 4.16.  | SDIO                          | 20 |

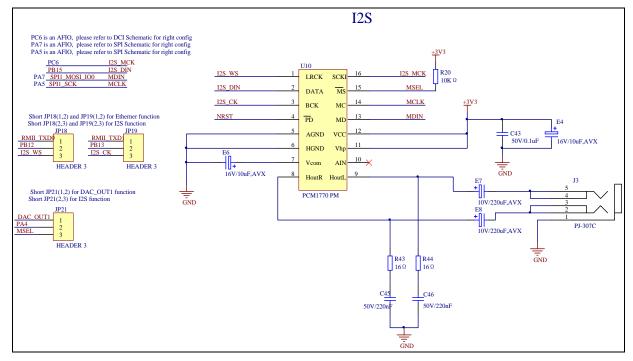

| 4.17.  | I2S                           | 20 |

| 4.18.  | SDRAM                         | 21 |

| 4.19.  | DCI                           | 22 |

| 4.20.  | Extension                     | 22 |

| 5. R0  | OUTINE USE GUIDE              | 23 |

| 5.1.   | GPIO running light            | 23 |

| 5.1.1  | . DEMO Purpose                | 23 |

| 5.1.2  | •                             |    |

| 5.1.3  | ·                             |    |

| 5.2.   | GPIO key polling mode         | 26 |

| 5.2.1  | . DEMO Purpose                | 26 |

| 5.2.2  | DEMO Principle                | 27 |

| 5.2.3  | B. DEMO Implementation Result | 30 |

| 5.3.   | GPIO key interrupt mode       | 30 |

| 5.3.1  | . DEMO Purpose                | 30 |

| 5.3.2  | DEMO Principle                | 31 |

| 5.3.3  | B. DEMO Implementation Result | 35 |

| 5.4. U | USART1_Printf                 | 36 |

| 5.4.1  | . DEMO Purpose                | 36 |

| 5.4.2  | DEMO Principle                | 38 |

| 5.4.3  | B. DEMO Implementation Result | 39 |

| 5.5.   | USART1_Echo_Interrupt_mode    | 40 |

| 5.5.1  | . DEMO Purpose                | 40 |

| 5.5.2  | DEMO Principle                | 42 |

| 5.5.3  | B. DEMO Implementation Result | 43 |

| 5.6. l | USART1_DMA                    | 44 |

| 5.6.1  | . DEMO Purpose                | 44 |

| 5.6.2  | DEMO Principle                | 45 |

| 5.6.3  | B. DEMO Implementation Result | 47 |

| 5.7. I | I2C read and write EEPROM     | 48 |

| 5.7.1  | . DEMO Purpose                | 48 |

| 5.7.2   | 2. DEMO Principle                                             | 48                      |

|---------|---------------------------------------------------------------|-------------------------|

| 5.7.3   | 3. DEMO Implementation Result                                 | 50                      |

| 5.8.    | SPI-Flash quad wire flash read and write                      | 51                      |

| 5.8.1   | •                                                             |                         |

| 5.8.2   | ·                                                             |                         |

| 5.8.3   | •                                                             |                         |

| 5.9.    | EXMC_NAND Flash                                               | 57                      |

| 5.9.1   | 1. DEMO Purpose                                               | 57                      |

| 5.9.2   | 2. DEMO Principle                                             | 58                      |

| 5.9.3   | 3. DEMO Implementation Result                                 | 63                      |

| 5.10.   | SDIO TF card test DEMO                                        | 64                      |

| 5.10.   | 0.1. DEMO Purpose                                             | 64                      |

| 5.10.   | 0.2. DEMO Principle                                           | 65                      |

| 5.10.   | 0.3. DEMO Implementation Result                               | 68                      |

| 5.11.   | RTC_Calendar                                                  | 69                      |

| 5.11.   | .1. DEMO Purpose                                              | 69                      |

| 5.11.   | .2. DEMO Principle                                            | 69                      |

| 5.11.   | .3. DEMO Implementation Result                                | 71                      |

| 5.12.   | ADC analog digital conversion, including internal temperature | re sensor and reference |

| voltage |                                                               |                         |

| 5.12.   | •                                                             |                         |

|         | 2.2. DEMO Principle                                           |                         |

| 5.12.   | 2.3. DEMO Implementation Result                               | 74                      |

| 5.13.   | DAC digital analog conversion                                 | 75                      |

| 5.13.   | 3.1. DEMO Purpose                                             | 75                      |

| 5.13.   | •                                                             |                         |

| 5.13.   | 3.3. DEMO Implementation Result                               | 76                      |

| 5.14.   | Controller Area Network (bxCAN)                               |                         |

| 5.14.   | •                                                             |                         |

| 5.14.   | •                                                             |                         |

| 5.14.   | 3. DEMO Implementation Result                                 | 83                      |

| 5.15.   | Cryptographic Acceleration Unit                               |                         |

| 5.15.   | ·                                                             |                         |

| 5.15.   | •                                                             |                         |

| 5.15.   | 5.3. DEMO Implementation Result                               | 86                      |

| 5.16.   | Hash Acceleration Unit                                        |                         |

| 5 16    | S.1 DEMO Purpose                                              | 97                      |

| 5.16.2  | . DEMO Principle                 | 88  |

|---------|----------------------------------|-----|

| 5.16.3  | DEMO Implementation Result       | 89  |

| 5.17.   | Random number generator (RNG)    | 90  |

| 5.17.1. | . , ,                            |     |

| 5.17.2  | ·                                |     |

| 5.17.3  | ·                                |     |

| 5.18.   | TLDI_without_GUI                 | 91  |

| 5.18.1. | . DEMO Purpose                   | 91  |

| 5.18.2  | . DEMO Principle                 | 92  |

| 5.18.3  | . DEMO Implementation Result     | 94  |

| 5.19.   | TAMPER and Waveform Detection    | 95  |

| 5.19.1  | . DEMO Purpose                   | 95  |

| 5.19.2  | DEMO principle                   | 95  |

| 5.19.3  | DEMO Implementation Result       | 97  |

| 5.20.   | USB OTG_FS virtual mouse         | 97  |

| 5.20.1  | . DEMO Purpose                   | 97  |

| 5.20.2  | DEMO Principle                   | 97  |

| 5.20.3  | DEMO implementation result       | 102 |

| 5.21.   | USB OTG_FS virtual U disk        | 102 |

| 5.21.1  | •                                |     |

| 5.21.2  | •                                |     |

| 5.21.3. | . DEMO Implementation Result     | 107 |

| 5.22.   | USB OTG_FS virtual ComPort (VCP) |     |

| 5.22.1. | . DEMO Purpose                   |     |

| 5.22.2. | •                                |     |

| 5.22.3  | . DEMO Implementation Result     | 113 |

| 5.23.   | USB OTG_FS MSC host              |     |

| 5.23.1. | ·                                |     |

| 5.23.2  | ·                                |     |

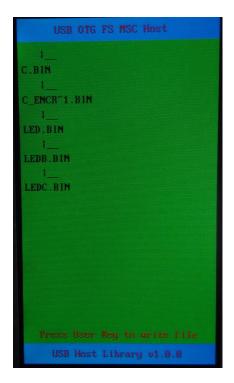

| 5.23.3  | DEMO Implementation Result       | 119 |

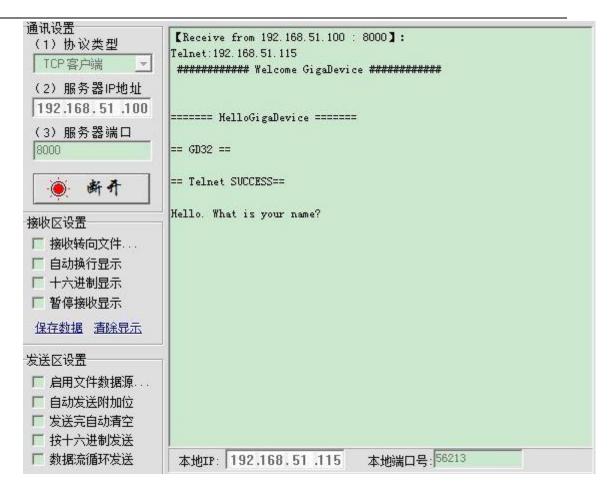

| 5.24.   | ETH                              |     |

| 5.24.1. | •                                |     |

| 5.24.2  | •                                |     |

| 5.24.3  | DEMO Implementation Result       | 128 |

| 5.25.   | EXMC_SDRAM                       | 131 |

| 5.25.1  | •                                |     |

| 5.25.2  | . DEMO Principle                 | 132 |

| 5.25.3. | DEMO Implementation Result | 137 |

|---------|----------------------------|-----|

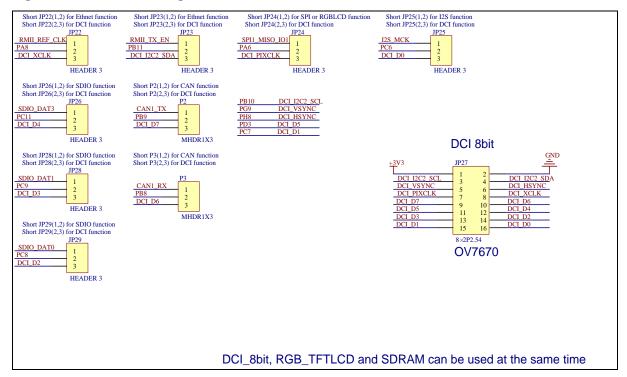

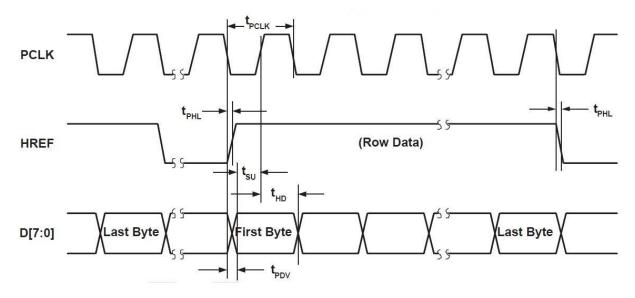

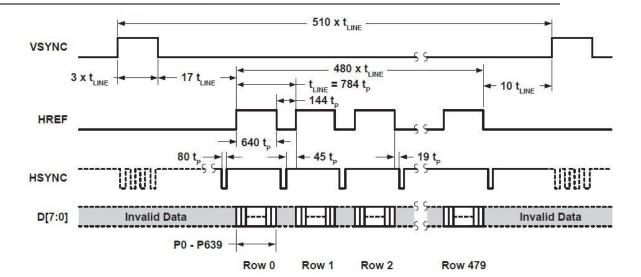

| 5.26. E | OCI Camera Capture         | 137 |

| 5.26.1. | DEMO Purpose               | 137 |

| 5.26.2. | DEMO Principle             | 138 |

| 5.26.3. | DEMO Implementation Result | 142 |

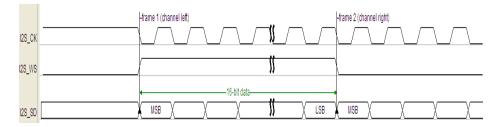

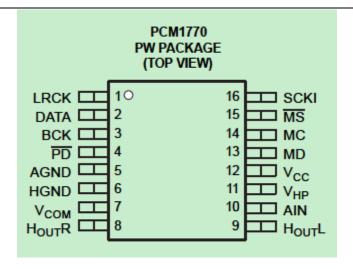

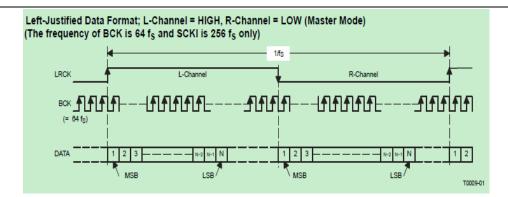

| 5.27. I | 2S Audio Play              | 143 |

| 5.27.1. | DEMO Purpose               | 143 |

| 5.27.2. | DEMO Principle             | 143 |

| 5.27.3. | DEMO Implementation Result | 147 |

| 6. REV  | ISION HISTORY              | 148 |

# **List of Figures**

| Figure 4-1 Schematic diagram of power supply                         |    |

|----------------------------------------------------------------------|----|

| Figure 4-2 Schematic diagram of boot option                          | 13 |

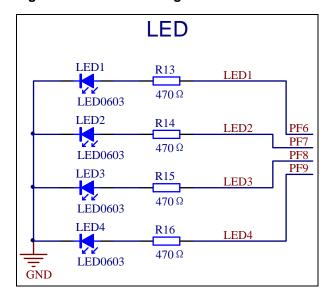

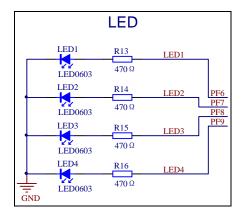

| Figure 4-3 Schematic diagram of LED function                         |    |

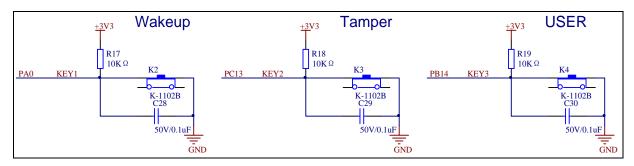

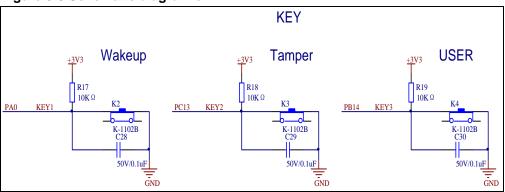

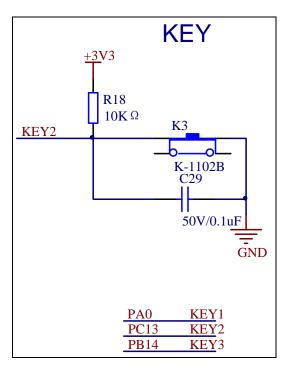

| Figure 4-4 Schematic diagram of Key function                         | 14 |

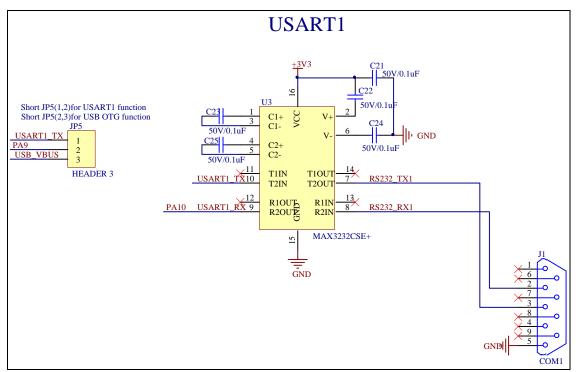

| Figure 4-5 Schematic diagram of USART1 function                      |    |

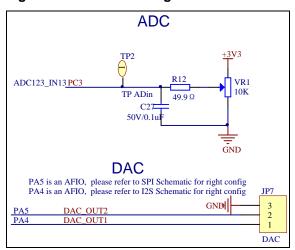

| Figure 4-6 Schematic diagram of ADC/DAC function                     | 15 |

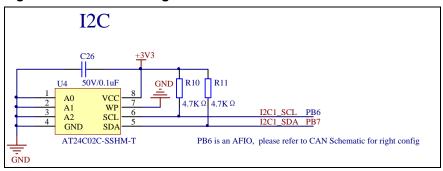

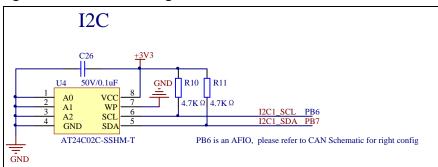

| Figure 4-7 Schematic diagram of I2C function                         | 15 |

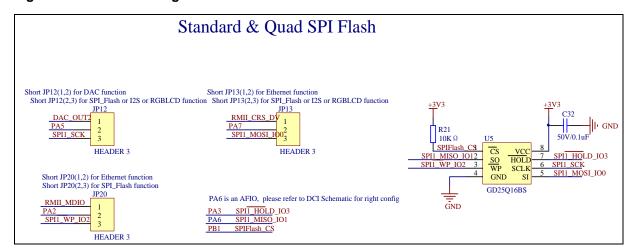

| Figure 4-8 Schematic diagram of SPI-Serial Flash function            | 16 |

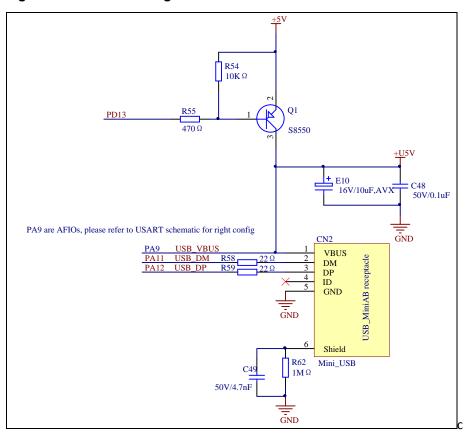

| Figure 4-9 Schematic diagram of USB function                         | 16 |

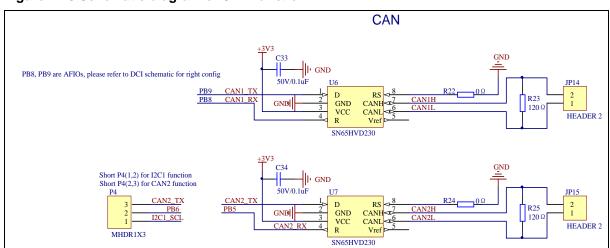

| Figure 4-10 Schematic diagram of CAN function                        |    |

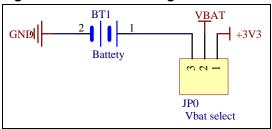

| Figure 4-11 Schematic diagram of RTC function                        | 17 |

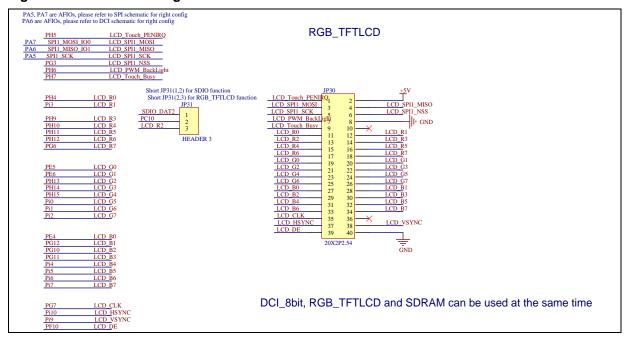

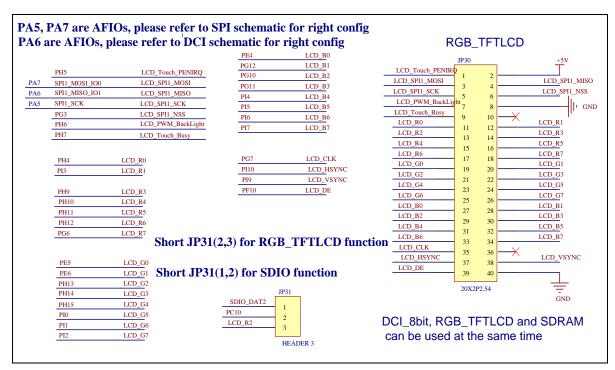

| Figure 4-12 Schematic diagram of TLDI RGB-LCD function               | 18 |

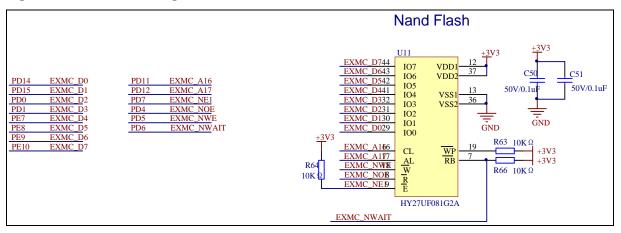

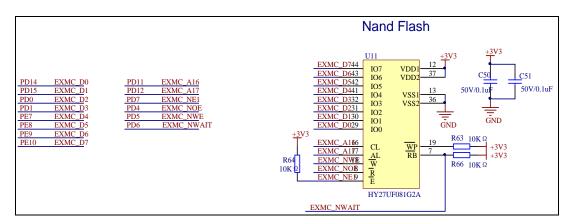

| Figure 4-13 Schematic diagram of EXMC-NAND Flash function            | 18 |

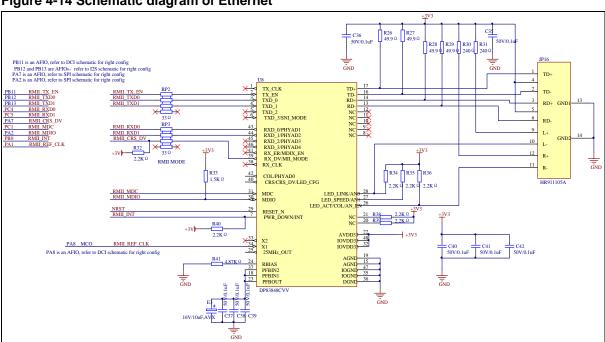

| Figure 4-14 Schematic diagram of Ethernet                            |    |

| Figure 4-15 Schematic diagram of GD-Link                             | 19 |

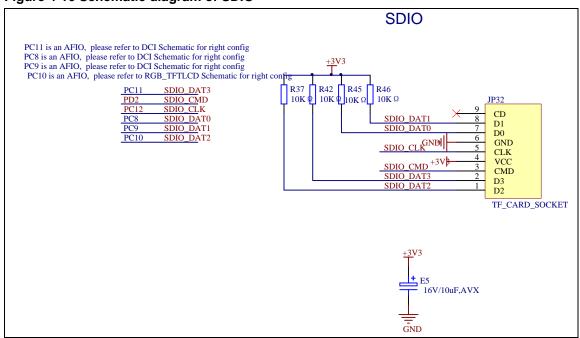

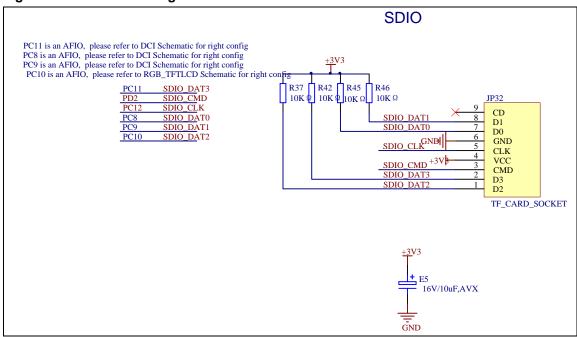

| Figure 4-16 Schematic diagram of SDIO                                | 20 |

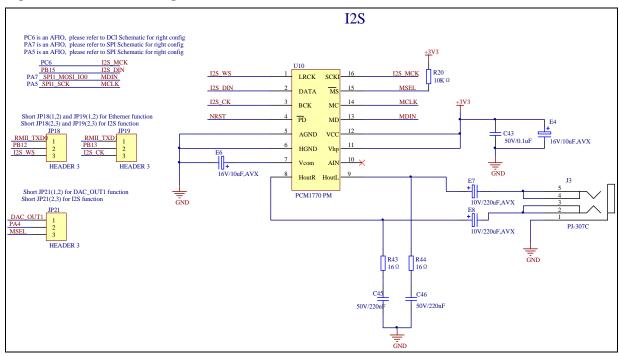

| Figure 4-17 Schematic diagram of I2S                                 | 20 |

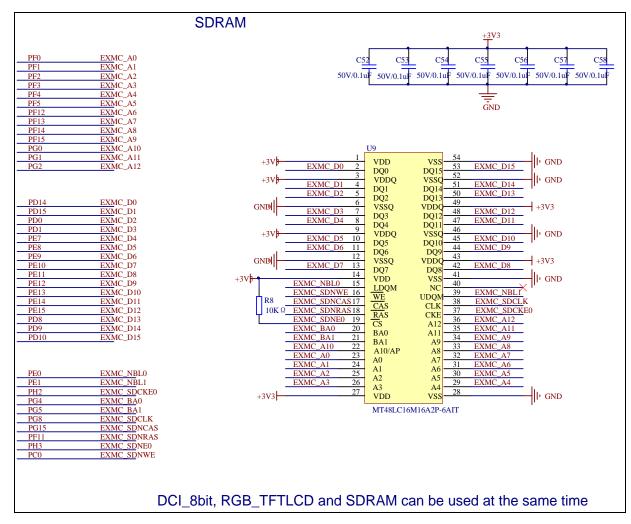

| Figure 4-18 Schematic diagram of SDRAM                               | 21 |

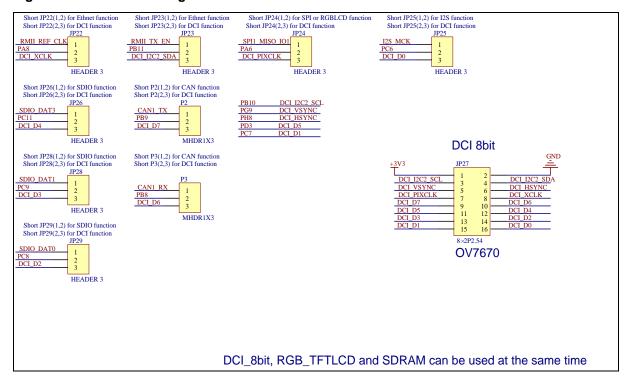

| Figure 4-19 Schematic diagram of DCI                                 | 22 |

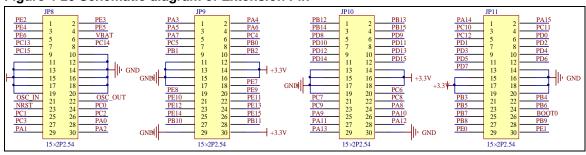

| Figure 4-20 Schematic diagram of Extension Pin                       | 22 |

| Figure 5-1 GPIO output driver block diagram                          | 24 |

| Figure 5-2 Schematic diagram of LED                                  | 25 |

| Figure 5-3 GPIO input drive block diagram                            |    |

| Figure 5-4 GPIO output driver block diagram                          |    |

| Figure 5-5 Schematic diagram of KEY                                  |    |

| Figure 5-6 Schematic diagram of LED                                  | 29 |

| Figure 5-7 GPIO input drive block diagram                            | 32 |

| Figure 5-8 GPIO output driver block diagram                          | 33 |

| Figure 5-9 Schematic diagram of KEY                                  | 33 |

| Figure 5-10 Schematic diagram of LED                                 | 34 |

| Figure 5-11 Block diagram of EXTI                                    | 35 |

| Figure 5-12 USART module block diagram                               | 38 |

| Figure 5-13 Schematic diagram of USART1                              | 39 |

| Figure 5-14 USART module block diagram                               |    |

| Figure 5-15 Schematic diagram of USART1                              |    |

| Figure 5-16 USART module block diagram                               | 46 |

| Figure 5-17 Schematic diagram of USART1                              | 47 |

| Figure 5-18 Schematic diagram of I2C                                 |    |

| Figure 5-19 SPI data clock timing in quad wire mode(SCKPL=1,SCKPH=0) | 53 |

| Figure 5-20 Schematic diagram of SPI                                 | 54 |

| Figure 5-21 Quad write operation timing diagram of GD25Q16B               | 55  |

|---------------------------------------------------------------------------|-----|

| Figure 5-22 The EXMC block diagram                                        | 59  |

| Figure 5-23 EXMC memory banks                                             | 60  |

| Figure 5-24 NAND address mapping                                          | 61  |

| Figure 5-25 Diagram of bank2 common space                                 | 61  |

| Figure 5-26 Schematic diagram of EXMC-NAND Flash function                 | 62  |

| Figure 5-27 Schematic diagram of SDIO                                     | 65  |

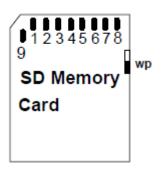

| Figure 5-28 SD Memory Card Shape and Interface                            | 66  |

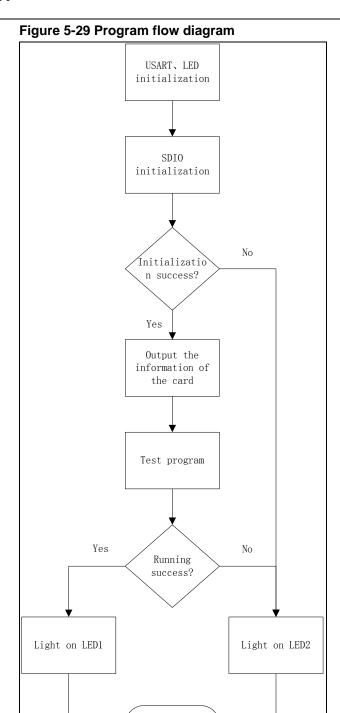

| Figure 5-29 Program flow diagram                                          | 67  |

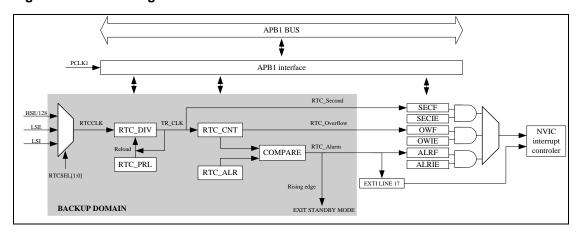

| Figure 5-30 Block diagram of RTC                                          |     |

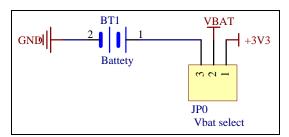

| Figure 5-31 Schematic diagram of RTC                                      | 70  |

| Figure 5-32 Schematic diagram of VBAT power supply                        | 71  |

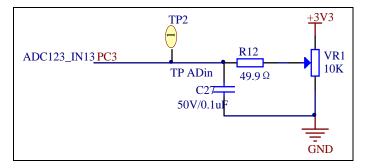

| Figure 5-33 Schematic diagram of ADC                                      | 73  |

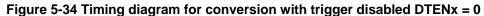

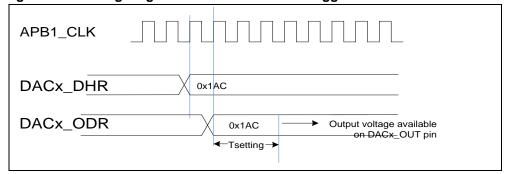

| Figure 5-34 Timing diagram for conversion with trigger disabled DTENx = 0 | 76  |

| Figure 5-35 Schematic diagram of DAC                                      |     |

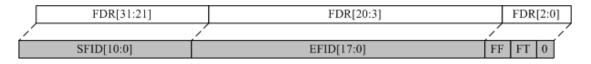

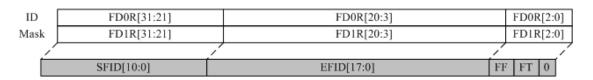

| Figure 5-36 CAN module block diagram                                      | 79  |

| Figure 5-37 32-bit filter                                                 | 80  |

| Figure 5-38 16-bit filter                                                 | 80  |

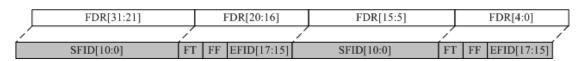

| Figure 5-39 32-bit mask mode filter                                       | 80  |

| Figure 5-40 32-bit list mode filter                                       | 81  |

| Figure 5-41 32-bit filter number                                          | 81  |

| Figure 5-42 Filtering index                                               | 82  |

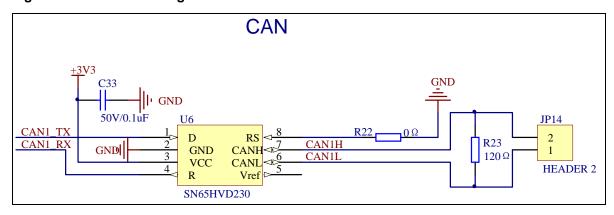

| Figure 5-43 Schematic diagram of CAN function                             |     |

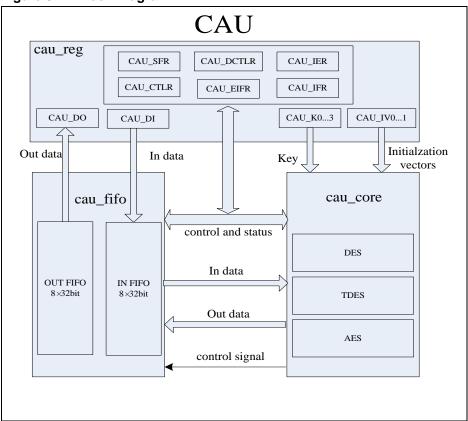

| Figure 5-44 Block Diagram                                                 | 85  |

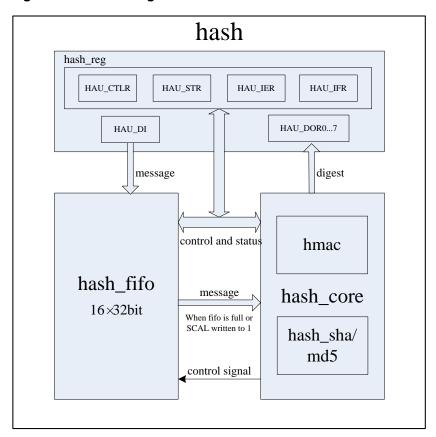

| Figure 5-45 Block Diagram                                                 |     |

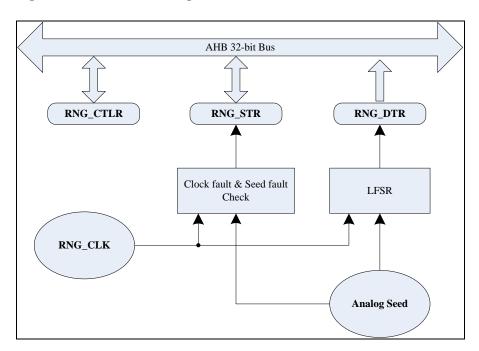

| Figure 5-46 RNG Block Diagram                                             | 90  |

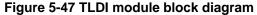

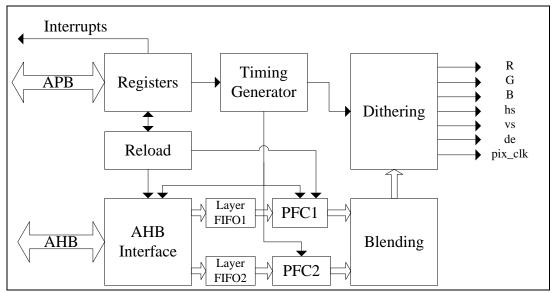

| Figure 5-47 TLDI module block diagram                                     | 93  |

| Figure 5-48 Schematic diagram of TLDI RGB-LCD function                    | 94  |

| Figure 5-49 Schematic diagram of KEY                                      | 96  |

| Figure 5-50 Schematic diagram of LED                                      | 97  |

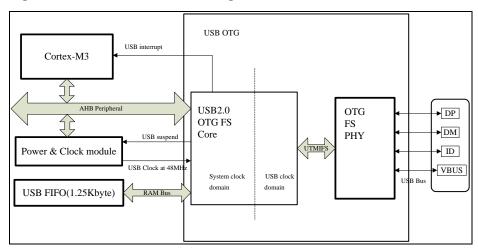

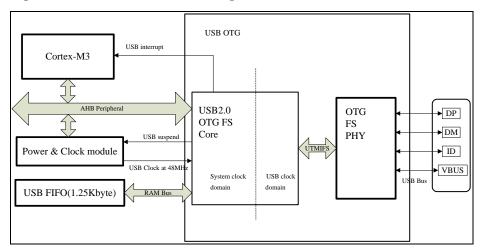

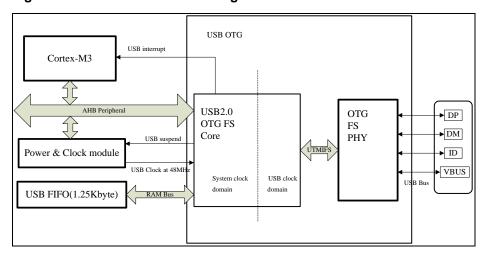

| Figure 5-51 USB OTG FS block diagram                                      | 100 |

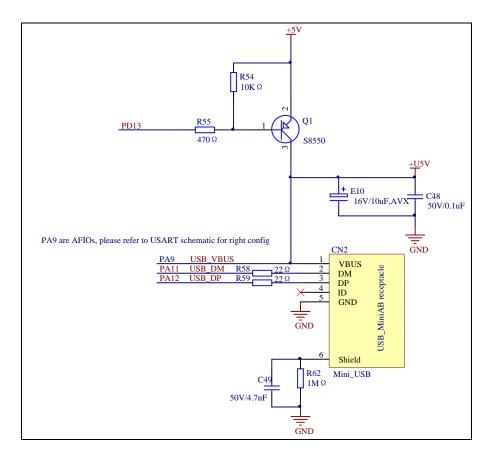

| Figure 5-52 Schematic diagram of USB                                      | 101 |

| Figure 5-53 USB OTG FS block diagram                                      | 105 |

| Figure 5-54 Schematic diagram of USB                                      | 107 |

| Figure 5-55 USB OTG FS block diagram                                      | 111 |

| Figure 5-56 Schematic diagram of USB                                      | 112 |

| Figure 5-57 USB OTG FS block diagram                                      | 117 |

| Figure 5-58 Schematic diagram of USB                                      | 118 |

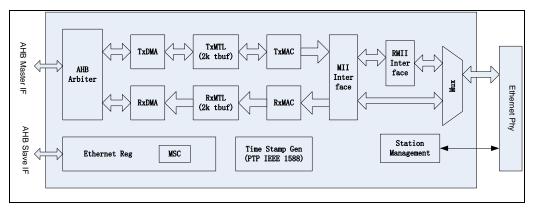

| Figure 5-59 ETH module block diagram                                      | 123 |

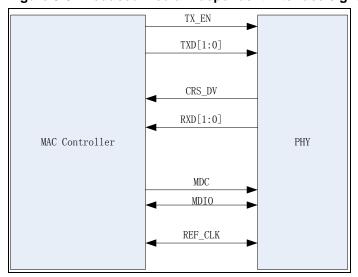

| Figure 5-60 Media independent interface signals                           | 125 |

| Figure 5-61 Reduced media-independent interface signals                   |     |

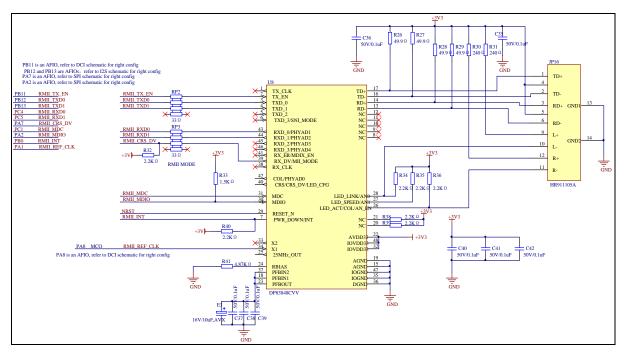

| Figure 5-62 Schematic diagram of Ethernet                                 | 128 |

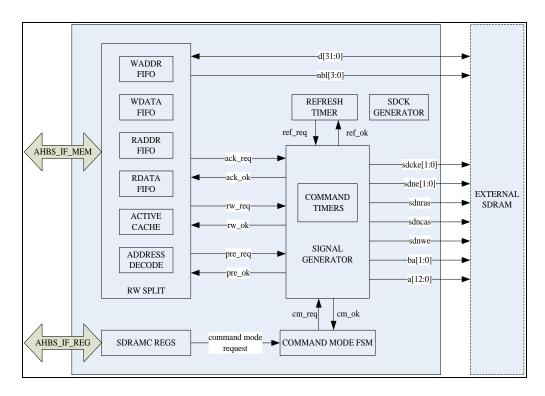

| Figure 5-63 The EXMC block diagram                                        | 133 |

| Figure 5-64 EXMC memory banks                                             | 134 |

#### User Manual GD32207I-EVAL

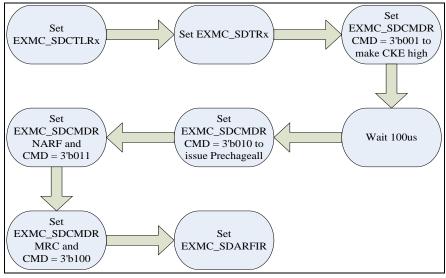

| Figure 5-65 SDRAMC block diagram                        |     |

|---------------------------------------------------------|-----|

| Figure 5-66 initialization sequence of SDRAM controller | 135 |

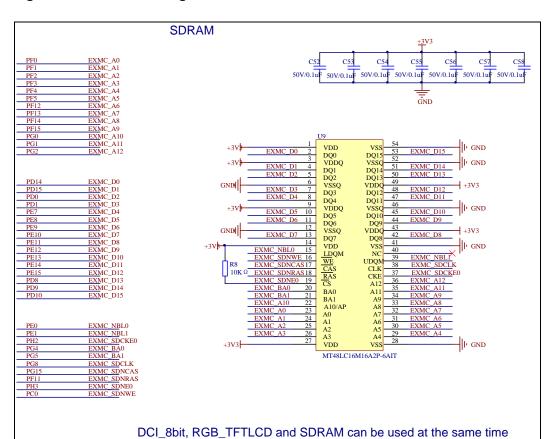

| Figure 5-67 Schematic diagram of SDRAM                  | 136 |

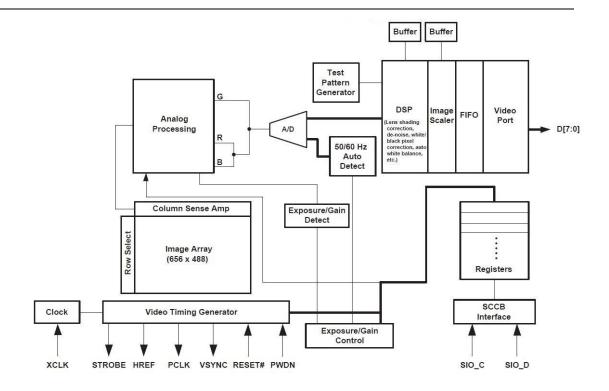

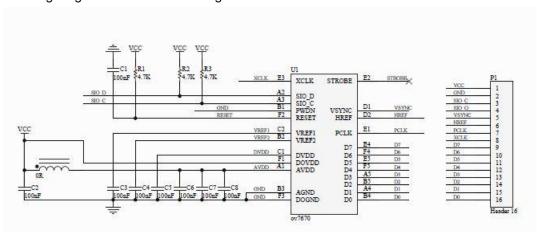

| Figure 5-68 Schematic diagram of DCI                    | 140 |

| Figure 5-69 Schematic diagram of I2S                    | 147 |

# **List of Tables**

| Table 2-1 Pin assignment                              | 8   |

|-------------------------------------------------------|-----|

| Table 4-1 Boot configuration                          | 13  |

| Table 5-1 USART important pins description            | 38  |

| Table 5-2 USART important pins description            | 42  |

| Table 5-3 USART important pins description            | 45  |

| Table 5-4 8-bit or 16-bit NAND Flash interface signal | 59  |

| Table 5-5 Command sets                                | 62  |

| Table 5-6 Address Cycle Map                           | 63  |

| Table 5-7 Memory card alternate-function              | 66  |

| Table 5-8 Clock range                                 | 124 |

| Table 5-9 SDRAM interface signal                      | 133 |

| Table 6-1. Revision history                           | 148 |

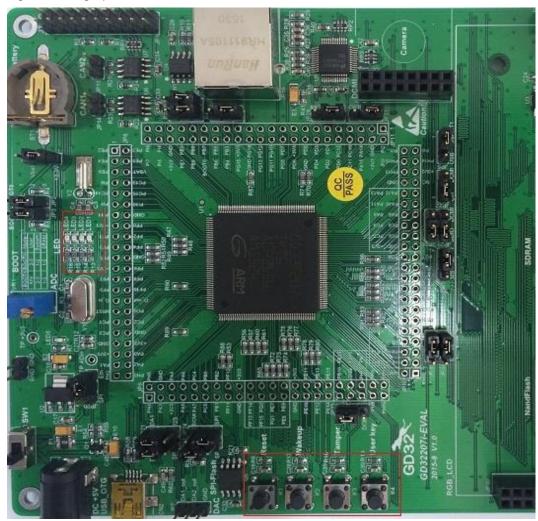

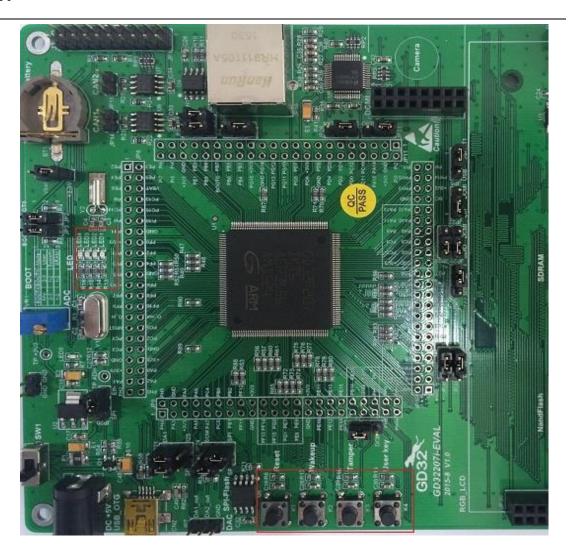

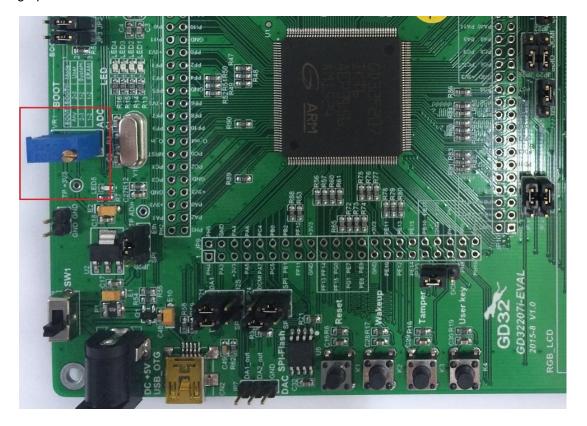

### 1. Introduction

GD32207I-EVAL evaluation board uses GD32F207IKT6 as the main controller. As a complete development platform of GD32F207xx connectivity line powered by ARM® Cortex™-M3 core, the board supports full range of peripherals. It uses Mini USB interface or AC/DC adapter as 5V power supply. JTAG, Reset, Boot, User button key, LED, CAN, I2C, I2S,DCI,SDRAM,USART, RTC, EXMC, SPI, USB\_OTG, ADC, DAC, GD-Link、TLDI RGB-LCD、SDIO, Ethernet and Extension Pin are also included. This document details its hardware schematic and the relevant applications.

## 2. Function pin assignment

**Table 2-1 Pin assignment**

| Function | Pin  | Description      |

|----------|------|------------------|

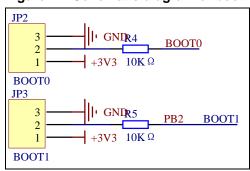

| LED      | PF6  | LED1             |

|          | PF7  | LED2             |

| LED      | PF8  | LED3             |

|          | PF9  | LED4             |

| RESET    |      | K1-Reset         |

|          | PA0  | KEY1             |

| KEY      | PC13 | KEY2             |

|          | PB14 | KEY3             |

|          | PA9  | USB_VBUS         |

| LICD OTC | PA11 | USB_DM           |

| USB_OTG  | PA12 | USB_DP           |

|          | PD13 | VBUS control pin |

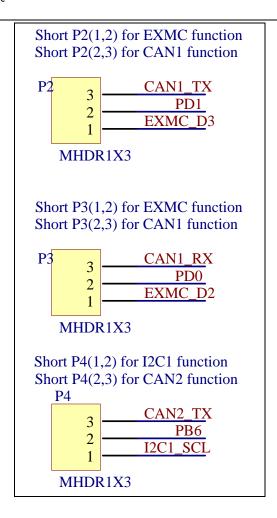

|          | PB8  | CAN1_RX          |

| CAN      | PB9  | CAN1_TX          |

| CAN      | PB5  | CAN2_RX          |

|          | PB6  | CAN2_TX          |

| 100      | PB6  | I2C1_SCL         |

| I2C      | PB7  | I2C1_SDA         |

|          | PB12 | I2S_WS           |

|          | PB15 | I2S_DIN          |

|          | PB13 | I2S_CK           |

| 128      | PC6  | I2S_MCK          |

|          | PA4  | MSEL             |

|          | PA5  | MCLK             |

|          | PA7  | MDIN             |

| Function | Pin   | Description   |

|----------|-------|---------------|

|          | RESET | NRST          |

|          | PA9   | USART1_TX     |

| USART1   | PA10  | USART1_RX     |

|          | PD14  | EXMC_D0       |

|          | PD15  | EXMC_D1       |

|          | PD0   | EXMC_D2       |

|          | PD1   | EXMC_D3       |

|          | PE7   | EXMC_D4       |

|          | PE8   | EXMC_D5       |

|          | PE9   | EXMC_D6       |

| EXMC     | PE10  | EXMC_D7       |

|          | PD11  | EXMC_A16      |

|          | PD12  | EXMC_A17      |

|          | PD4   | EXMC_NOE      |

|          | PD5   | EXMC_NWE      |

|          | PD6   | EXMC_NWAIT    |

|          | PD7   | EXMC_NE1      |

|          | PA2   | SPI1_WP_IO2   |

|          | PA3   | SPI1_HOLD_IO3 |

|          | PA5   | SPI1_SCK      |

| SPI      | PA6   | SPI1_MISO_IO1 |

|          | PA7   | SPI1_MOSI_IO0 |

|          | PB1   | SPIFlash_CS   |

| ADC      | PC3   | ADC123_IN13   |

| 210      | PA4   | DAC_OUT1      |

| DAC      | PA5   | DAC_OUT2      |

|          | PC12  | SDIO_CLK      |

|          | PD2   | SDIO_CMD      |

| 0010     | PC8   | SDIO_DAT0     |

| SDIO     | PC9   | SDIO_DAT1     |

|          | PC10  | SDIO_DAT2     |

|          | PC11  | SDIO_DAT3     |

|          | PC6   | DCI_D0        |

|          | PC7   | DCI_D1        |

|          | PC8   | DCI_D2        |

|          | PC9   | DCI_D3        |

| DCI      | PC11  | DCI_D4        |

|          | PD3   | DCI_D5        |

|          | PB8   | DCI_D6        |

|          | PB9   | DCI_D7        |

|          | PA6   | DCI_PIXCLK    |

| Function   | Pin  | Description       |

|------------|------|-------------------|

|            | PA8  | DCI_XCLK          |

|            | PG9  | DCI_VSYNC         |

|            | PH8  | DCI_HSYNC         |

|            | PB10 | DCI_I2C2_SCL      |

|            | PB11 | DCI_I2C2_SDA      |

|            | PH4  | LCD_R0            |

|            | Pi3  | LCD_R1            |

|            | PC10 | LCD_R2            |

|            | PH9  | LCD_R3            |

|            | PH10 | LCD_R4            |

|            | PH11 | LCD_R5            |

|            | PH12 | LCD_R6            |

|            | PG6  | LCD_R7            |

|            | PE5  | LCD_G0            |

|            | PE6  | LCD_G1            |

|            | PH13 | LCD_G2            |

|            | PH14 | LCD_G3            |

|            | PH15 | LCD_G4            |

|            | Pi0  | LCD_G5            |

|            | Pi1  | LCD_G6            |

|            | Pi2  | LCD_G7            |

|            | PE4  | LCD_B0            |

| RGB_TFTLCD | PG12 | LCD_B1            |

|            | PG10 | LCD_B2            |

|            | PG11 | LCD_B3            |

|            | Pi4  | LCD_B4            |

|            | Pi5  | LCD_B5            |

|            | Pi6  | LCD_B6            |

|            | Pi7  | LCD_B7            |

|            | PG7  | LCD_CLK           |

|            | Pi10 | LCD_HSYNC         |

|            | PF10 | LCD_DE            |

|            | Pi9  | LCD_VSYNC         |

|            | PH7  | LCD_Touch_Busy    |

|            | PH6  | LCD_PWM_BackLight |

|            | PA5  | LCD_SPI1_SCK      |

|            | PA7  | LCD_SPI1_MOSI     |

|            | PH5  | LCD_Touch_PENIRQ  |

|            | PG3  | LCD_SPI1_NSS      |

|            | PA6  | LCD_SPI1_MISO     |

| SDARM      | PD14 | EXMC_D0           |

| Function | Pin  | Description |

|----------|------|-------------|

|          | PD15 | EXMC_D1     |

|          | PD0  | EXMC_D2     |

|          | PD1  | EXMC_D3     |

|          | PE7  | EXMC_D4     |

|          | PE8  | EXMC_D5     |

|          | PE9  | EXMC_D6     |

|          | PE10 | EXMC_D7     |

|          | PE11 | EXMC_D8     |

|          | PE12 | EXMC_D9     |

|          | PE13 | EXMC_D10    |

|          | PE14 | EXMC_D11    |

|          | PE15 | EXMC_D12    |

|          | PD8  | EXMC_D13    |

|          | PD9  | EXMC_D14    |

|          | PD10 | EXMC_D15    |

|          | PF0  | EXMC_A0     |

|          | PF1  | EXMC_A1     |

|          | PF2  | EXMC_A2     |

|          | PF3  | EXMC_A3     |

|          | PF4  | EXMC_A4     |

|          | PF5  | EXMC_A5     |

|          | PF12 | EXMC_A6     |

|          | PF13 | EXMC_A7     |

|          | PF14 | EXMC_A8     |

|          | PF15 | EXMC_A9     |

|          | PG0  | EXMC_A10    |

|          | PG1  | EXMC_A11    |

|          | PG2  | EXMC_A12    |

|          | PE0  | EXMC_NBL0   |

|          | PE1  | EXMC_NBL1   |

|          | PH2  | EXMC_SDCKE0 |

|          | PG4  | EXMC_BA0    |

|          | PG5  | EXMC_BA1    |

|          | PG8  | EXMC_SDCLK  |

|          | PG15 | EXMC_SDNCAS |

|          | PF11 | EXMC_SDNRAS |

|          | PH3  | EXMC_SDNE0  |

|          | PC0  | EXMC_SDNWE  |

|          | PB11 | RMII_TX_EN  |

| Ethernet | PB12 | RMII_TXD0   |

|          | PB13 | RMII_TXD1   |

| Function | Pin | Description  |

|----------|-----|--------------|

|          | PC4 | RMII_RXD0    |

|          | PC5 | RMII_RXD1    |

|          | PA7 | RMII_CRS_DV  |

|          | PC1 | RMII_MDC     |

|          | PA2 | RMII_MDIO    |

|          | PB0 | RMII_INT     |

|          | PA1 | RMII_REF_CLK |

## 3. Getting started

The EVAL Board uses Mini USB connecter or adapter to get power, the hardware system power is +3.3V. A Mini USB cable and a J-Link tool are necessary to down programs. Select the correct boot mode and then power on, the LED5 will turn on, which indicates the power supply is ready.

## 4. Hardware layout overview

## 4.1. Power supply

Figure 4-1 Schematic diagram of power supply

## 4.2. Boot option

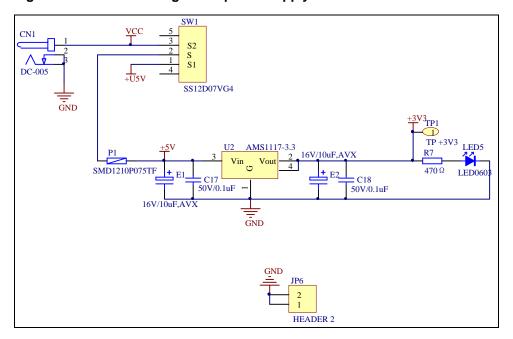

Figure 4-2 Schematic diagram of boot option

**Table 4-1 Boot configuration**

| BOOT1 | ВООТ0 | Boot Mode     |

|-------|-------|---------------|

| Any   | 2-3   | User memory   |

| 2-3   | 1-2   | System memory |

| 1-2   | 1-2   | SRAM memory   |

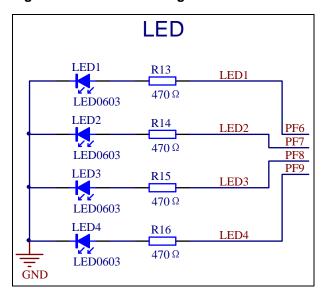

### 4.3. LED

Figure 4-3 Schematic diagram of LED function

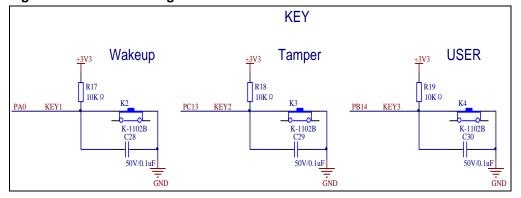

## 4.4. Key

Figure 4-4 Schematic diagram of Key function

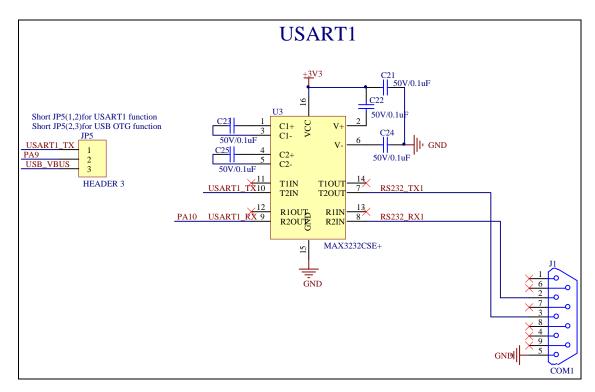

#### 4.5. **USART1**

Figure 4-5 Schematic diagram of USART1 function

### 4.6. ADC/DAC

Figure 4-6 Schematic diagram of ADC/DAC function

### 4.7. I2C

Figure 4-7 Schematic diagram of I2C function

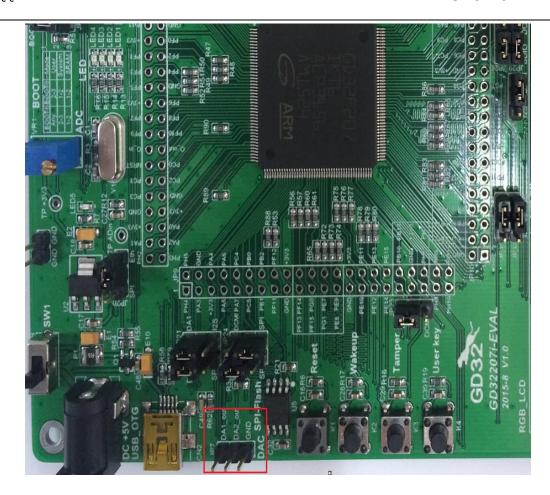

#### 4.8. SPI-Serial Flash

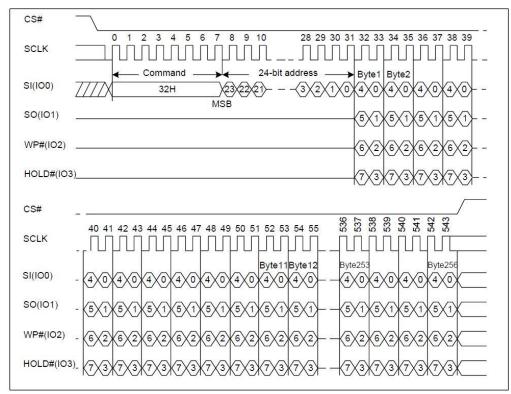

Figure 4-8 Schematic diagram of SPI-Serial Flash function

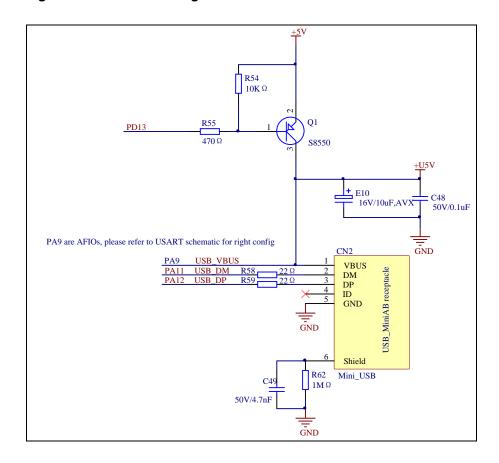

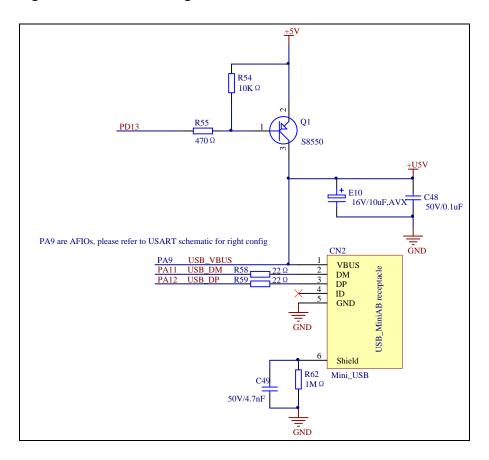

#### 4.9. USB

Figure 4-9 Schematic diagram of USB function

## 4.10. CAN

Figure 4-10 Schematic diagram of CAN function

### 4.11. RTC

Figure 4-11 Schematic diagram of RTC function

#### 4.12. TLDI RGB-LCD

Figure 4-12 Schematic diagram of TLDI RGB-LCD function

#### 4.13. EXMC-NAND Flash

Figure 4-13 Schematic diagram of EXMC-NAND Flash function

#### 4.14. **Ethernet**

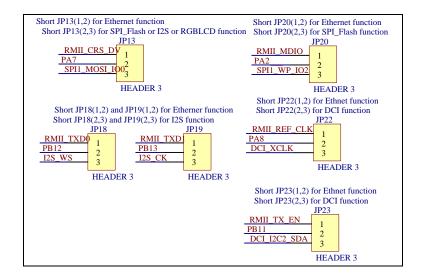

Figure 4-14 Schematic diagram of Ethernet

#### 4.15. **GD-Link**

Figure 4-15 Schematic diagram of GD-Link

| PA15 |

|------|

| PA13 |

| PA14 |

| PB3  |

| NRST |

|      |

#### 4.16. SDIO

Figure 4-16 Schematic diagram of SDIO

#### 4.17. I2S

Figure 4-17 Schematic diagram of I2S

#### 4.18. SDRAM

Figure 4-18 Schematic diagram of SDRAM

#### 4.19. DCI

Figure 4-19 Schematic diagram of DCI

#### 4.20. Extension

Figure 4-20 Schematic diagram of Extension Pin

## 5. Routine use guide

#### 5.1. GPIO running light

#### 5.1.1. DEMO Purpose

GD32207I-EVAL-V1.0 development board has four LED lights:LED1, LED2, LED3 and LED4. This DEMO will show you how to control the effect of four LED lights flashing in implementation of running water. Also the DEMO will tell you the demonstration of GD32F20X internal GPIO configuration method, and shows you GPIO output characteristic. The key is how to control the IO output different levels of this DEMO, and then the LED flashing, in this DEMO, you will master the basic use of GD32F20X GPIO.

#### GD32F20X GPIO main features:

- Input/output direction control

- Each pin weak pull-up/pull-down function

- Output push-pull/open drain enable control

- Output set/reset control

- External interrupt with programmable trigger edge using EXTI configuration registers

- Analog input/output configurations

- Alternate function input/output configurations

- Port configuration lock

#### 5.1.2. **DEMO Principle**

GD32F20X GPIO port can be configured into 8 modes by software:

- Analog input

- Floating input

- Pull-up input

- Pull-down input

- Open-drain output

- Push-pull output

- Alternate Open-drain output

- Alternate Push-pull output

```

Corresponding to the GD32 library file is defined as follows: typedef enum

{

GPIO_MODE_AIN = 0x0,

GPIO_MODE_IN_FLOATING = 0x04,

GPIO_MODE_IPD = 0x28,

GPIO_MODE_IPU = 0x48,

GPIO_MODE_OUT_OD = 0x14,

GPIO_MODE_OUT_PP = 0X10,

GPIO_MODE_AF_OD = 0X1C,

GPIO_MODE_AF_PP = 0X18

```

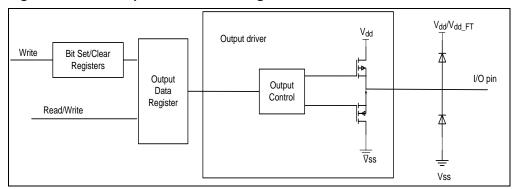

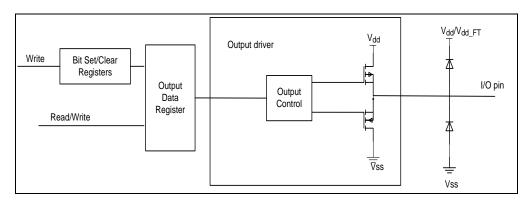

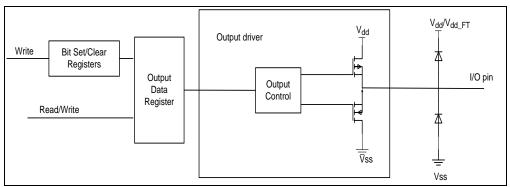

Figure 5-1 GPIO output driver block diagram

}GPIO\_ModePara;

Note:  $V_{dd\_FT}$  is dedicated for five-volt tolerant I/Os and is different from  $V_{dd}$

When GPIO pin is configured as output:

- The Schmitt Trigger Input is activated.

- The weak pull-up and pull-down resistors are disabled.

- The Output Buffer is enabled:

Open Drain Mode: a "0" in the output register activates the N-MOS while a "1" in the Output register leaves the port in Hi-Z.

Push-Pull Mode: a "0" in the output register activates the N-MOS while a "1" in the Output register activates the P-MOS.

- Read the Data Output Register gets the last written value in Push-Pull mode

- Read the Data Input Register gets the I/O state in open drain mode

The GPIO is configured as a push-pull output, and in order to realize the effect of light water, the IO output is controlled by the GPIO setting or resetting function. When the port is set, the GPIO output will be high, and the LED will light, When the port is reset, the GPIO output will be low, and the LED will be off.

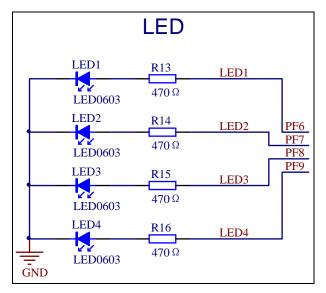

Figure 5-2 Schematic diagram of LED

The above shows the LED circuit diagram, where the resistance of the LED series, in series with the LED is mainly used to limit the current to avoid damaging the LED and the GPIO port.

#### 5.1.3. **DEMO Implementation Result**

Download the program to the development board, the implementation of the results is the development board LED1 will be the light first, and then off, and LED2 be light So LED1, LED2, LED3, LED4 are successfully be light in a flow. One of the LED switch to another every 500ms to achieve the function of running light water. The position of the four LEDs are shown in the red region of the graph.

## 5.2. GPIO key polling mode

#### 5.2.1. **DEMO Purpose**

GD32207I-EVAL-V1.0 development board has four keys: K1 (Reset), K2 (Wakeup), K3 (Tamper), K4 (User Key). In this Demo, only K3 (Temper) is used. This Demo will introduce the GD32F20X GPIO Input function, and demonstrate the GD32F20X internal GPIO configuration method, show the GPIO input characteristics.

#### GD32F20X GPIO main features:

- Input/output direction control

- Each pin weak pull-up/pull-down function

- Output push-pull/open drain enable control

- Output set/reset control

- External interrupt with programmable trigger edge using EXTI configuration registers

- Analog input/output configurations

- Alternate function input/output configurations

- Port configuration lock

#### 5.2.2. DEMO Principle

GD32F20X GPIO port can be configured into 8 modes of software:

- Analog input

- Floating input

- Pull-up input

- Pull-down input

- Open-drain output

- Push-pull output

- Alternate Open-drain output

- Alternate Push-pull output

Corresponding to the GD32 library file is defined as follows:

```

typedef enum

{

GPIO_MODE_AIN = 0x0,

GPIO_MODE_IN_FLOATING = 0x04,

GPIO_MODE_IPD = 0x28,

GPIO_MODE_IPU = 0x48,

GPIO_MODE_OUT_OD = 0x14,

GPIO_MODE_OUT_PP = 0X10,

GPIO_MODE_AF_OD = 0X1C,

GPIO_MODE_AF_PP = 0X18

}GPIO_MODE_AF_PP = 0X18

```

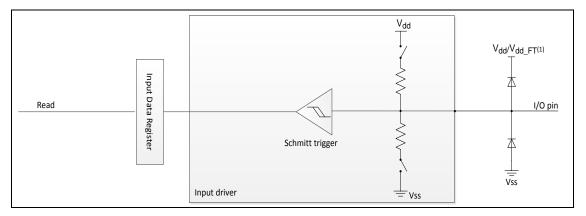

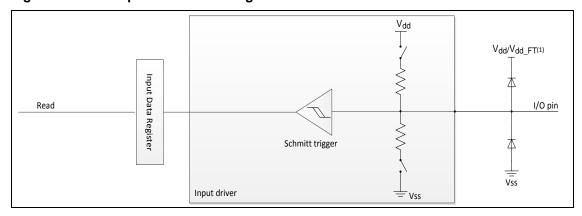

Figure 5-3 GPIO input drive block diagram

Note: V<sub>dd\_FT</sub> is dedicated for five-volt tolerant I/Os and is different from V<sub>dd</sub>

When GPIO pin is configured as Input:

- The Schmitt Trigger Input is activated

- The weak pull-up and pull-down resistors could be chosen

- The data present on the I/O pad is sampled into the data input register every APB2 clock cycle

- The Output Buffer is disabled

Figure 5-4 GPIO output driver block diagram

Note: Vdd\_FT is dedicated for five-volt tolerant I/Os and is different from Vdd

When GPIO pin is configured as output:

- The Schmitt Trigger Input is activated.

- The weak pull-up and pull-down resistors are disabled.

- The Output Buffer is enabled:

Open Drain Mode: a "0" in the output register activates the N-MOS while a "1" in the Output register leaves the port in Hi-Z.

Push-Pull Mode: a "0" in the output register activates the N-MOS while a "1" in the

Output register activates the P-MOS.

- Read the Data Output Register gets the last written value in Push-Pull mode

- Read the Data Input Register gets the I/O state in open drain mode

In this DEMO floating input mode is adopted, and external pull up resistance is used, Refer to the output driver block diagram, the GPIO is configured as a floating input. When the key is pressed down, read the data input register if the data is zero, then delay some time and read pin data input register again, if the data is one, It means that the key pressing is not successful, it is still be zero, then the key pressing is successful, and the LED2 toggles.

Figure 5-5 Schematic diagram of KEY

The GPIO is configured as a push-pull output, and in order to realize the effect of light water, the IO output is controlled by the GPIO setting or resetting function. When the port is set, the GPIO output will be high, and the LED will light, When the port is reset, the GPIO output will be low, and the LED will be off.

Figure 5-6 Schematic diagram of LED

The above shows the LED circuit diagram, where the resistance of the LED series, in series with the LED is mainly used to limit the current to avoid reducing LED use age.

#### 5.2.3. **DEMO Implementation Result**

Download the program to the development board, the phenomenon is that the K3 be pressed down the first time in the development board, and LED1 turns on. and K3 be pressed down the second time, LED1 turns off. The position of the four LEDs and K3 is shown in the red region of the graph.

## 5.3. GPIO key interrupt mode

#### 5.3.1. DEMO Purpose

GD32207I-EVAL-V1.0 development board has four keys: K1 (Reset), K2 (Wakeup), K3 (Tamper), K4 (User Key). In this DEMO, only K3 (Temper) is used. This DEMO will introduce the external interrupt characteristics of GD32F20X port, demonstrate the configuration method of GD32F20X GPIO external interrupt, and show the GPIO external interrupt characteristics. For EXTI principle learning.

#### GD32F20X GPIO main features:

- Input/output direction control

- Each pin weak pull-up/pull-down function

- Output push-pull/open drain enable control

- Output set/reset control

- External interrupt with programmable trigger edge using EXTI configuration registers

- Analog input/output configurations

- Alternate function input/output configurations

- Port configuration lock

#### GD32F20X EXTI main features:

- Cortex-M3 system exception

- Up to 90maskable peripheral interrupts

- 4 bits interrupt priority configuration—16 priority levels

- Efficient interrupt processing

- Support exception pre-emption and tail chaining

- Wake up system from power saving mode

- 20 independent edge detectors in EXTI

- Three trigger types: rising, falling and both edges

- Software interrupt or event trigger

- Trigger sources configurable

#### 5.3.2. **DEMO Principle**

GD32F20X GPIO port can be configured into 8 modes of software:

- Analog input

- Floating input

- Pull-up input

- Pull-down input

- Open-drain output

- Push-pull output

- Alternate Open-drain output

#### Alternate Push-pull output

```

Corresponding to the GD32 library file is defined as follows:

```

```

typedef enum

{

GPIO_MODE_AIN = 0x0,

GPIO_MODE_IN_FLOATING = 0x04,

GPIO_MODE_IPD = 0x28,

GPIO_MODE_IPU = 0x48,

GPIO_MODE_OUT_OD = 0x14,

GPIO_MODE_OUT_PP = 0X10,

GPIO_MODE_AF_OD = 0X1C,

GPIO_MODE_AF_PP = 0X18

}GPIO_MODE_AF_PP = 0X18

```

Figure 5-7 GPIO input drive block diagram

Note:  $V_{dd\_FT}$  is dedicated for five-volt tolerant I/Os and is different from  $V_{dd}$

When GPIO pin is configured as Input:

- The Schmitt Trigger Input is activated

- The weak pull-up and pull-down resistors could be chosen

- The data present on the I/O pad is sampled into the data input register every APB2 clock cycle

- The Output Buffer is disabled

Figure 5-8 GPIO output driver block diagram

Note: V<sub>dd\_FT</sub> is dedicated for five-volt tolerant I/Os and is different from V<sub>dd</sub>

When GPIO pin is configured as output:

- The Schmitt Trigger Input is activated.

- The weak pull-up and pull-down resistors are disabled.

- The Output Buffer is enabled:

Open Drain Mode: a "0" in the output register activates the N-MOS while a "1" in the Output register leaves the port in Hi-Z.

Push-Pull Mode: a "0" in the output register activates the N-MOS while a "1" in the Output register activates the P-MOS.

- Read the Data Output Register gets the last written value in Push-Pull mode

- Read the Data Input Register gets the I/O state in open drain mode

In this DEMO floating input mode is adopted, and external pull up resistance is used, Refer to the output driver block diagram, The GPIO is configured to the falling edge trigged of an external interrupt. If the key (K3) is pressed down, an external interrupt will occur. In the external interrupt service function, the LED2 toggles.

Figure 5-9 Schematic diagram of KEY

The GPIO is configured as a push-pull output, and in order to realize the effect of light water, the IO output is controlled by the GPIO setting or resetting function. When the port is set, the GPIO output will be high, and the LED will light. When the port is reset, the GPIO output will

be low, and the LED will be off.

Figure 5-10 Schematic diagram of LED

The above shows the LED circuit diagram, where the resistance of the LED

series, in series with the LED is mainly used to limit the current to avoid damaging the LED and the GPIO port.

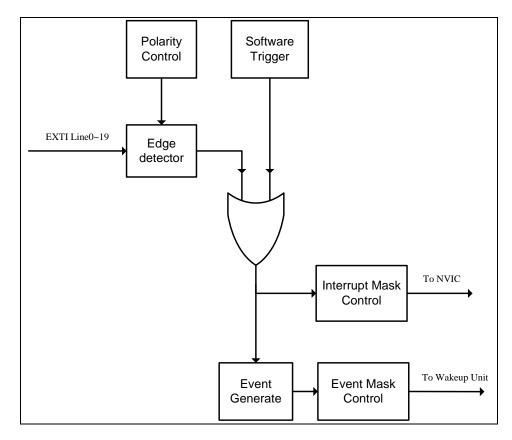

External Interrupt and Event(EXTI)The EXTI contains 20 independent edge detectors and generates interrupts request or wake up event to the processer. The EXTI has three trigger types: rising edge, falling edge and both edges. Each edge detector in the EXTI can be configured and masked independently. Figure below is the block diagram of EXTI.

Figure 5-11 Block diagram of EXTI

The EXTI trigger source includes 16 external lines from GPIO pins and 4 lines from internal modules (including LVD, RTC Alarm, USB Wake-up and Ethernet Wake-up, please), but this four EXTI lines are connected to the external trigger. All GPIO pins can be selected as an EXTI trigger source by configuring AFIO\_ESSRx registers in GPAFIO module (please refer to GPIOs and AFIOs section for detail).

EXTI can provide not only interrupts but also event signals to the process. The Cortex-M3 processor fully implements the Wait For Interrupt (WFI), Wait For Event (WFE) and the Send Event (SEV) instructions. The GD32F20x include a Wake-up Interrupt Controller (WIC). This enables the processor and NVIC to be put into a very low-power sleep mode leaving the WIC to identify and prioritize interrupts and event. EXTI can be used to wake up processor and the whole system when some expected event occurs, such as a special GPIO pin toggling or RTC alarm.

### 5.3.3. **DEMO Implementation Result**

Download the program to the development board, the phenomenon is that the K3 be pressed down the first time in the development board, and LED1 turns on. And K3 be pressed down the second time, LED1 turns off. The position of the four LEDs and K3 is shown in the red region of the graph.

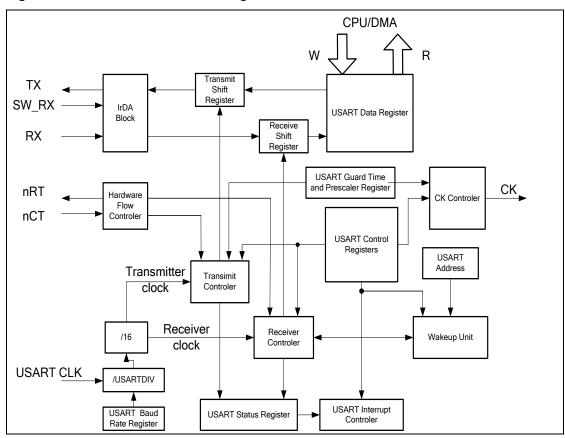

# 5.4. USART1\_Printf

## 5.4.1. DEMO Purpose

GD32207I-EVAL-V1.0 board extract USART1 (Universal synchronous asynchronous receiver transmitter). GD32F207IKT6 hold 8 serial port, this Demo set USART1 for example, to show GD32F20X series USART print features and using method.

#### GD32F20X USART main features:

- Full duplex, asynchronous communications

- Half duplex single wire communications

- NRZ standard format (Mark/Space)

- Programmable baud-rate generator allowing speeds up to 7.5 MBits/s when the clock frequency is120 MHz and oversampling is by 16.

- Fully programmable serial interface characteristics:

- Even, odd or no-parity bit generation/detection

- A data word length can be 8 or 9 bits

- 1, 1.5 or 2 stop bit generation

- Configurable data polarity

- Hardware Modem operations (CTS/RTS)

- Configurable multi-buffer communication using centralized DMA

- Separate enable bits for Transmitter and Receiver

- Transfer detection flags:

- Receive buffer full

- Transmit buffer empty

- End of Transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Error detection: Overrun, Noise, Frame and Parity error

- LIN Break generation and detection

- IrDA Support

- Synchronous mode and transmitter clock output for synchronous transmission

- ISO 7816-3 (T=0 and T=1) compliant smart card interface

- Multiprocessor communication

- Enter into mute mode if address match does not occur

- Wake up from mute mode by idle line or address mark detection

- Support for ModBus communication

- Timeout feature

- CR/LF character recognition

- 12 interrupt sources with flags:

- CTS changes

- LIN break detection

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line detected

- Overrun error

- Framing error

- Noise error

- Parity error

- Receiver timeout interrupt

- End of block interrupt

While USART1/2/3/6 is fully implemented, UART4/5/7/8 is only partially implemented with the following features not supported.

- Smartcard mode

- Synchronous mode

- Hardware Modem operations (CTS/RTS)

- Configurable data polarity

## 5.4.2. **DEMO Principle**

Table 5-1 USART important pins description

| Pin  | Туре                       | Description                            |

|------|----------------------------|----------------------------------------|

| RX   | Input                      | Receive Data                           |

| TX   | Output                     | Transmit Data. high level When         |

|      | I/O (single-wire/smartcard | enabled but nothing to be transmitted  |

|      | mode)                      |                                        |

| CK   | Output                     | Serial clock for synchronous           |

|      |                            | communication                          |

| nCTS | Input                      | Clear to send in Hardware flow control |

|      |                            | mode                                   |

| nRTS | Output                     | Request to send in Hardware flow       |

|      |                            | control mode                           |

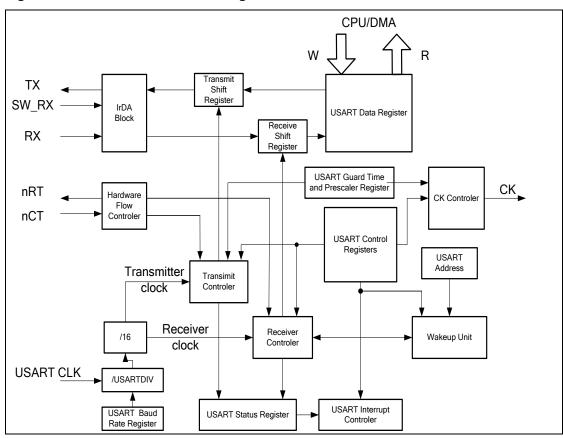

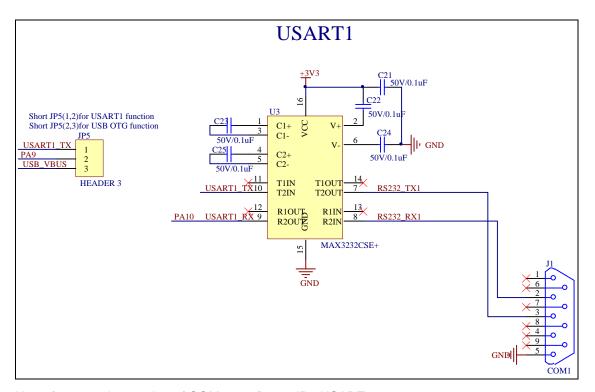

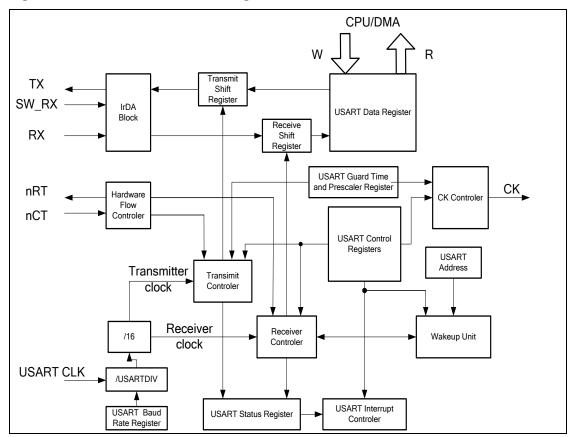

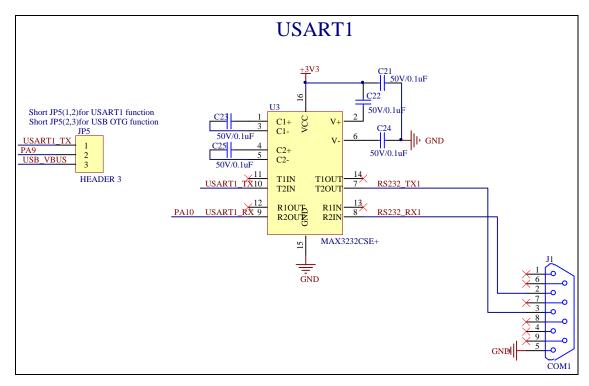

Figure 5-12 USART module block diagram

This DEMO realize print function, GD32F207I\_EVAL board get through RS232 connect to computer for communication.

According to the following steps, USART transmit data.

- 1. Write the WL bit in USART\_CTLR1 to set the data bits length

- 2. Set the stop bits length in USART\_CTLR2

- 3. Set the baud rate in USART\_BRR.

- 4. Set the UEN bit in USART\_CTLR1 to enable the USART

- 5. Set the TEN bit in USART\_CTLR1.

- 6. Wait for the TBE set

- 7. Write the data to in the USART\_DR register

- 8. Wait until TC=1 to finish

This routine hardware principle diagram is shown as following.

Figure 5-13 Schematic diagram of USART1

Note: for normal operation of COM1, configure JP5 USART1.

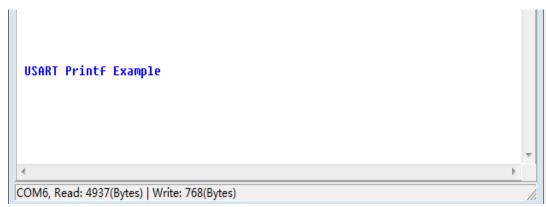

## 5.4.3. **DEMO Implementation Result**

After downloading program to board, Information via a serial port output as following.

```

USART Printf Example: Please press the Key

```

Press K2 key, serial port output as following.

# 5.5. USART1\_Echo\_Interrupt\_mode

## 5.5.1. DEMO Purpose

GD32207I-EVAL-V1.0 board extract USART1 (Universal synchronous asynchronous receiver transmitter). GD32F207 IKT6 hold 8 serial port, this DEMO set USART1 for example, to show GD32F20X series USART interrupt features and using method.

#### GD32F20X USART main features:

- Full duplex, asynchronous communications

- Half duplex single wire communications

- NRZ standard format (Mark/Space)

- Programmable baud-rate generator allowing speeds up to 7.5 MBits/s when the clock frequency is120 MHz and oversampling is by 16.

- Fully programmable serial interface characteristics:

- Even, odd or no-parity bit generation/detection

- A data word length can be 8 or 9 bits

- 1, 1.5 or 2 stop bit generation

- Configurable data polarity

- Hardware Modem operations (CTS/RTS)

- Configurable multi-buffer communication using centralized DMA

- Separate enable bits for Transmitter and Receiver

- Transfer detection flags:

- Receive buffer full

- Transmit buffer empty

- End of Transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Error detection: Overrun, Noise, Frame and Parity error

- LIN Break generation and detection

- IrDA Support

- Synchronous mode and transmitter clock output for synchronous transmission

- ISO 7816-3 (T=0 and T=1) compliant smart card interface

- Multiprocessor communication

- Enter into mute mode if address match does not occur

- Wake up from mute mode by idle line or address mark detection

- Support for ModBus communication

- Timeout feature

- CR/LF character recognition

- 12 interrupt sources with flags:

- CTS changes

- LIN break detection

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line detected

- Overrun error

- Framing error

- Noise error

- Parity error

- Receiver timeout interrupt

- End of block interrupt

While USART1/2/3/6 is fully implemented, UART4/5/7/8 is only partially implemented with the following features not supported.

- Smartcard mode

- Synchronous mode

- Hardware Modem operations (CTS/RTS)

- Configurable data polarity

## 5.5.2. **DEMO Principle**

Table 5-2 USART important pins description

| Pin  | Туре                       | Description                            |

|------|----------------------------|----------------------------------------|

| RX   | Input                      | Receive Data                           |

| TX   | Output                     | Transmit Data. high level When         |

|      | I/O (single-wire/smartcard | enabled but nothing to be transmitted  |

|      | mode)                      |                                        |

| CK   | Output                     | Serial clock for synchronous           |

|      |                            | communication                          |

| nCTS | Input                      | Clear to send in Hardware flow control |

|      |                            | mode                                   |

| nRTS | Output                     | Request to send in Hardware flow       |

|      |                            | control mode                           |

Figure 5-14 USART module block diagram

GD32F20X USART support full duplex interrupt transmission function, this DEMO transmit interrupt and receive data at the same time.

According to the following steps, USART transmit and receive interrupt.

- 1. Write the WL bit in USART\_CTLR1 to set the data bits length

- 2. Set the stop bits length in USART\_CTLR2

- 3. Set the baud rate in USART\_BRR.

- 4. Set the UEN bit in USART\_CTLR1 to enable the USART

- 5. Set the TEN bit and REN bit in USART CTLR1.

- 6. Configure USART1 interrupt, enable USART transmit and receive interrupt.

- 7. Wait for transmit and receive finish, compare TxBuffer and RxBuffer.

This routine hardware principle diagram is shown as following.

Figure 5-15 Schematic diagram of USART1

Note: for normal operation of COM1, configure JP5 USART1.

#### 5.5.3. **DEMO Implementation Result**

This DEMO firstly transmit 256 byte data and wait for receiving then 256 byte data verify. If the transmitted data are same with the received data, LED on the board will be on in turn, otherwise blink meanwhile.

After downloading program to board, Information via a serial port output as following, Then transmitted 256 byte data by the serial assistant software. Observe LED on the board, if data send and data receive is same verify correctly, LED on the board will be on in turn, otherwise blink meanwhile.

```

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17

18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F

30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D 3E 3F 40 41 42 43 44 45 46 47

48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F

60 61 62 63 64 65 66 67 68 69 6A 6B 6C 6D 6E 6F 70 71 72 73 74 75 76 77

78 79 7A 7B 7C 7D 7E 7F 80 81 82 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F

90 91 92 93 94 95 96 97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3 A4 A5 A6 A7

A8 A9 AA AB AC AD AE AF B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 BA BB BC BD BE BF

C0 C1 C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7

D8 D9 DA DB DC DD DE DF E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB EC ED EE EF

F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

```

## 5.6. USART1\_DMA

## 5.6.1. DEMO Purpose

GD32207I-EVAL-V1.0 board extract USART1 (Universal synchronous asynchronous receiver transmitter). GD32F207 IKT6 hold 8 serial port, this DEMO set USART1 for example, to show GD32F20X series USART DMA features and using method.

#### GD32F20X USART main features:

- Full duplex, asynchronous communications

- Half duplex single wire communications

- NRZ standard format (Mark/Space)

- Programmable baud-rate generator allowing speeds up to 7.5 MBits/s when the clock frequency is120 MHz and oversampling is by 16.

- Fully programmable serial interface characteristics:

- Even, odd or no-parity bit generation/detection

- A data word length can be 8 or 9 bits

- 1, 1.5 or 2 stop bit generation

- Configurable data polarity

- Hardware Modem operations (CTS/RTS)

- Configurable multi-buffer communication using centralized DMA

- Separate enable bits for Transmitter and Receiver

- Transfer detection flags:

- Receive buffer full

- Transmit buffer empty

- End of Transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Error detection: Overrun, Noise, Frame and Parity error

- LIN Break generation and detection

- IrDA Support

- Synchronous mode and transmitter clock output for synchronous transmission

- ISO 7816-3 (T=0 and T=1) compliant smart card interface

- Multiprocessor communication

- Enter into mute mode if address match does not occur

- Wake up from mute mode by idle line or address mark detection

- Support for ModBus communication

- Timeout feature

- CR/LF character recognition

- 12 interrupt sources with flags:

- CTS changes

- LIN break detection

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line detected

- Overrun error

- Framing error

- Noise error

- Parity error

- Receiver timeout interrupt

- End of block interrupt

While USART1/2/3/6 is fully implemented, UART4/5/7/8 is only partially implemented with the following features not supported.

- Smartcard mode

- Synchronous mode

- Hardware Modem operations (CTS/RTS)

- Configurable data polarity

## 5.6.2. **DEMO Principle**

Table 5-3 USART important pins description

| Pin  | Туре                       | Description                            |

|------|----------------------------|----------------------------------------|

| RX   | Input                      | Receive Data                           |

| TX   | Output                     | Transmit Data. high level When         |

|      | I/O (single-wire/smartcard | enabled but nothing to be transmitted  |

|      | mode)                      |                                        |

| CK   | Output                     | Serial clock for synchronous           |

|      |                            | communication                          |

| nCTS | Input                      | Clear to send in Hardware flow control |

|      |                            | mode                                   |

| nRTS | Output                     | Request to send in Hardware flow       |

control mode

#### Figure 5-16 USART module block diagram

GD32F20X USART support DMA transmit function, this DEMO transmit and receive data in independent DMA channel. This DEMO firstly transmit 256 byte data and wait for receiving then verify.

According to the following steps,

- 1. Write the WL bit in USART\_CTLR1 to set the data bits length

- 2. Set the stop bits length in USART\_CTLR2

- 3. Set the baud rate in USART\_BRR.

- 4. Set the UEN bit in USART\_CTLR1 to enable the USART

- 5. Set the TEN bit and REN bit in USART\_CTLR1.

- 6. Configure DMA, enable DMA corresponding channel, enable USART DMAtransmit and receive.

- 7. Wait for transmit and receive finish, compare TxBuffer and RxBuffer.

This routine hardware principle diagram is shown as following.

Figure 5-17 Schematic diagram of USART1

Note: for normal operation of COM1, configure JP5 USART1.

### 5.6.3. **DEMO Implementation Result**

This DEMO firstly transmit 256 byte data and wait for receiving then 256 byte data verify. If the transmitted data are same with the received data, LED on the board will be on in turn, otherwise blink meanwhile.

After downloading program to board, Information via a serial port output as following, Then transmitted 256 byte data by the serial assistant software. Observe LED on the board, if data send and data receive is same as well verify correctly, LED on the board will be on in turn, otherwise blink meanwhile.

```

1F

21

22 23 24 25

26

27

38 39

3A 3B 3C 3D 3E 3F 40 41 42 43 44 45 46

50 51 52 53 54 55 56 57

6A

6B 6C 6D 6E 6F 70 71

72

73

64

65 66

67

68 69

80

81

82

83

84

85

86

87

88

89

7B

7C

7D

7E

7F

9A

9D

B3 B4 B5 B6 B7 B8 B9 BA BB BC BD BE BF

B1 B2

CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7

C0 C1 C2 C3 C4 C5 C6 C7

C8 C9

D8 D9 DA DB DC DD DE DF E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB EC ED EE EF

FØ F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

```

### 5.7. I2C read and write EEPROM

### 5.7.1. **DEMO Purpose**

GD32207I-EVAL-V1.0 board integrated the I2C (circuit inter-integrated) module, and the module provides an I2C interface which is an industry standard two line serial interface for MCU to communicate with external I2C interface. In this Demo, putting the common AT24C02C-SSHM-T chip with the I2C interface as the access object, through the DEMO, we can have an in-depth understanding of the I2C bus, and then master how to read and write the EEPROM interface I2C.

#### GD32F20X I2C main features:

- Parallel-bus to I2C-bus protocol converter and interface

- Both master and slave functions with the same interface

- Bi-directional data transfer between master and slave

- Supports 7-bit and 10-bit addressing and general call addressing

- Multi-master capability

- Supports Standard Speed (up to 100 kHz) and Fast Speed (up to 400 kHz)

- Configurable SCL stretching in slave mode

- Supports DMA mode

- SMBus 2.0 and PMBus compatible

- 2 Interrupts: one for successful byte transmission and the other for error event

- Optional PEC (packet error checking) generation and check

### 5.7.2. **DEMO Principle**

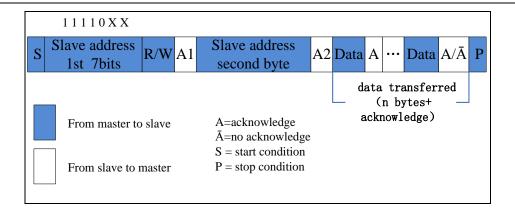

AT24C02C-SSHM-T access interface is I2C interface. The I2C module has two external lines, the serial data SDA and serial clock SCL lines. The two wires carry information between the devices connected to the bus. Both SDA and SCL are bidirectional lines. Data on the I2C-bus can be transferred at rates of up to 100 kbit/s in the standard-mode and up to 400 kbit/s in the fast mode.

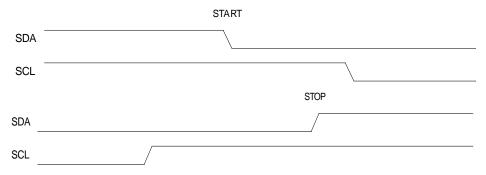

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred. As shown in the figure below:

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition. As shown in the figure below:

#### I2C communication flow:

Each I2C device is recognized by a unique address (whether it is a microcontroller, LCD driver, memory or keyboard interface) and can operate as either a transmitter or receiver, depending on the function of the device.

An I2C slave will continue to detect addresses after a start condition on I2C bus and compare the detected address with its own address which is programmable by software. Once the two addresses matches, the I2C slave will send an ACK to the I2C bus and responses to the following command on I2C bus: transmitting or receiving desired data. Additionally, if General Call is enabled by software, an I2C slave always responses to a General Call Address (0x00). The I2C block support both 7-bit and 10-bit addresses.

An I2C master always initiates or end a transfer using Start or Stop condition and it's also responsible for SCL clock generation.

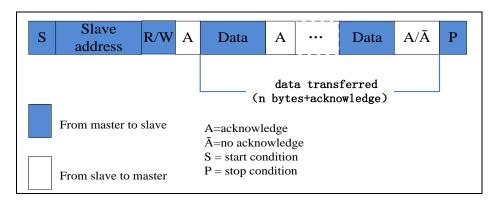

I2C communication flow with 7-bit address:

I2C communication flow with 10-bit address:

In this DEMO, the board GD32207I-EVAL-V1.0 comes with EEPROM AT24C02C-SSHM-T, and the chip capacity is 2Kbit. The board through the processor comes with the hardware I2C1 interface and the EEPROM connection. Circuit diagram as follows:

Figure 5-18 Schematic diagram of I2C

In this DEMO, firstly through the I2C interface write 256 bytes of data to EEPROM, and then read our just written into the data. Compare the data written and read the data is consistent. In the experiment the data to read, etc will be printed out through the serial port. Before the experiment using the jumper cap to connect P4(1,2).

### 5.7.3. DEMO Implementation Result

Download procedures, and under normal circumstances, serial print out the following information:

```

GD32207C-EVAL-VI.0 System is Starting up...

GD32207C-EVAL-VI.0 Program Version number: GD1.0

GD32207C-EVAL-VI.0 Program Compile time: (Sep. 9 2015 - 09:33:44)

GD32207C-EVAL-VI.0 GD32F20x_StdFeripA_Version:1.0.0

GD32207C-EVAL-V1.0 SystemCoreClock:120000000Hz

GD32207C-EVAL-V1.0 Flash:512K Bytes

GD32207C-EVAL-V1.0 The CPU Unique Device ID:[36353133-8343433-54350F3C]

GD32207C-EVAL-V1.0 I2C-24C02 configured.

The I2C1 is Hardware interface

------> The Speed is 40000AT24C02 Writing...0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0A 0x0B 0x0C 0x0D 0x0E 0x0F

0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1A 0x1B 0x1C 0x1D 0x1E 0x1F 0x20 0x21 0x22 0x23 0x24 0x25 0x26 0x27 0x28 0x29

0x2A 0x2B 0x2C 0x2D 0x2E 0x2F 0x3F 0x30 0x31 0x32 0x33 0x34 0x35 0x36 0x37 0x38 0x39 0x3A 0x3B 0x3C 0x3D 0x3E 0x3F 0x40 0x41 0x42 0x43

0x44 0x45 0x46 0x47 0x48 0x49 0x4A 0x4B 0x4C 0x4D 0x4E 0x4F 0x50 0x51 0x52 0x53 0x54 0x55 0x56 0x57 0x58 0x59 0x5A 0x5B 0x5C 0x5D 0x5D 0x5A

0x5E 0x5F 0x60 0x61 0x62 0x63 0x64 0x65 0x66 0x67 0x68 0x69 0x6A 0x6B 0x6C 0x6D 0x6E 0x6F 0x70 0x71 0x72 0x73 0x74 0x75 0x76 0x77

0x78 0x79 0x7A 0x7B 0x7C 0x7D 0x7E 0x7F 0x80 0x81 0x82 0x83 0x84 0x85 0x86 0x87 0x88 0x89 0x8A 0x8B 0x8C 0x8D 0x8E 0x8F 0x90 0x91

0x92 0x93 0x94 0x95 0x96 0x97 0x98 0x99 0x9A 0x9E 0x9C 0x9D 0x9E 0x9F 0xAO 0xA1 0xA2 0xA3 0xA4 0xA5 0xA6 0xA7 0xA8 0xA8 0xAA 0xAA

OMAC OMAD OMAE OMAE OMBO OMBI OMB2 OMB3 OMB4 OMB5 OMB6 OMB7 OMB8 OMB9 OMBA OMBB OMBC OMBD OMBE OMBF OMCO OMCI OMC2 OMC3 OMC4 OMC5

OXC6 OXC7 OXC8 OXC9 OXCA OXCB OXCC OXCD OXCE OXCF OXD0 OXD1 OXD2 OXD3 OXD4 OXD5 OXD6 OXD7 OXD8 OXD9 OXDA OXDB OXDC OXDD OXDE OXDF

OxFA OxFB OxFC OxFD OxFE OxFF

AT24C02 Reading...0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0A 0x0B 0x0C 0x0D 0x0E 0x0F 0x10 0x11 0x12 0x13 0x14 0x15

0x16 0x17 0x18 0x19 0x1A 0x1B 0x1C 0x1D 0x1E 0x1F 0x2O 0x21 0x22 0x23 0x24 0x25 0x26 0x27 0x28 0x29 0x2A 0x2B 0x2C 0x2E 0x2E 0x2E 0x2E 0x30 0x31 0x32 0x33 0x34 0x35 0x36 0x37 0x38 0x39 0x38 0x39 0x3A 0x3B 0x3C 0x3D 0x3E 0x3F 0x4O 0x41 0x42 0x43 0x44 0x45 0x46 0x47 0x48 0x49

0x4A 0x4B 0x4C 0x4D 0x4E 0x4F 0x50 0x51 0x52 0x53 0x54 0x55 0x56 0x57 0x58 0x59 0x5A 0x5B 0x5C 0x5D 0x5E 0x5F 0x60 0x61 0x62 0x63 0x64 0x65 0x66 0x67 0x68 0x67 0x68 0x69 0x6A 0x6B 0x6C 0x6D 0x6E 0x6F 0x70 0x71 0x72 0x73 0x74 0x75 0x76 0x77 0x78 0x79 0x7A 0x7B 0x7C 0x7D 0x7E 0x7F 0x60 0x81 0x82 0x81 0x82 0x83 0x84 0x85 0x86 0x87 0x88 0x89 0x8A 0x8B 0x8C 0x8D 0x8E 0x8F 0x90 0x91 0x92 0x93 0x94 0x95 0x96 0x97

Ox98 Ox99 Ox9A Ox9B Ox9C Ox9D Ox9E Ox9F OxAO OxA1 OxA2 OxA3 OxA4 OxA5 OxA6 OxA7 OxA8 OxA9 OxAA OxAB OxAC OxAD OxAE OxAF OxBO OxB1

OXEG OXET OXES OXES OXES OXED OXED OXED OXEE OXEF OXFO OXF1 OXF2 OXF3 OXF4 OXF5 OXF6 OXF7 OXF8 OXF9 OXFA OXFB OXFC OXFD OXFE OXFF

I2C-AT24CO2 Test Passed!

```

Firstly print some information on the board, data to written and data to read out,

and then print the results of the written data and read the results are consistent.

Program from address 0x00 sequential writes 256 bytes of data to the EEPROM, then program from address 0x00 order to read 256 bytes of data. To compare the data and read the data read, if the same, serial print out "Test Passed I2C-AT24C02!", while the board of the four LED lights flashing, otherwise serial print out "Read and Write are't Matching. Err:Data", while the four LED fight fully.

## 5.8. SPI-Flash quad wire flash read and write

#### 5.8.1. DEMO Purpose

This Demo use SPI1 interface of GD32207I-EVAL-V1.0 development board to read and write SPI NOR FLASH at quad SPI mode. The SPI NOR FLASH is a serial FLASH memory chip GD25Q16B which size is 16Mbit ,the chip supports standard SPI and quad SPI operation instructions.

GD32F20X SPI main features:

- Master or slave operation

- Quad wire configuration available in master mode

- Programmable clock bit rate

- Programmable clock polarity and phase

- Separate transmit and receive buffer, 16 bits wide

- Programmable data frame size, 8 or 16 bits

- Programmable data order, transmit MSB-first or LSB-first

- Hardware CRC calculation and transmit automatic CRC error checking

- Full-duplex synchronous transfers on three lines

- Simplex synchronous transfers on two lines

- NSS work in software mode or hardware mode for both master and slave

- SPI bus busy status flag

- Transmission and reception flags with interrupt capability

- Master configuration fault, overrun and CRC error flags with interrupt capability

- Transmission and reception by DMA capability

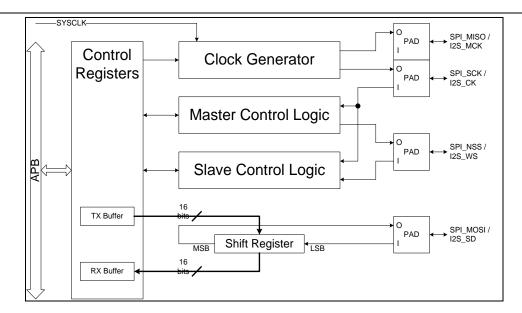

### 5.8.2. **DEMO Principle**

#### **Quad SPI principle**

In quad wire configuration, SPI uses 6 pins: MOSI, MISO, IO2, IO3, SCK and NSS.

MOSI: This pin is used to transmit data in quad write mode and receive data in quad read mode.

MISO: This pin is used to transmit data in quad write mode and receive data in quad read mode.

IO2: This pin is used to transmit data in quad write mode and receive data in quad read mode.

IO3: This pin is used to transmit data in quad write mode and receive data in quad read mode.

SCK: The configuration and behavior of SCK pin is the same as single wire mode except that there are only 2 clock cycles per data frame in quad wire configuration.

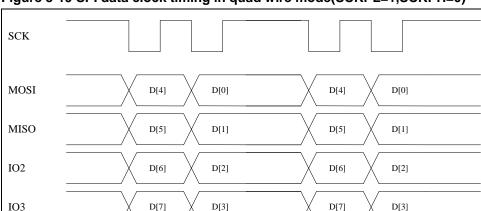

Data frame format: The frame length is fixed to 8 bit in quad wire mode, as shown below.

NSS: when this pin is driven low means external chip is selected.

The following figure is SPI data clock timing in quad wire mode(SCKPL=1,SCKPH=0)

Figure 5-19 SPI data clock timing in quad wire mode(SCKPL=1,SCKPH=0)

### SPI FLASH principle:

According to the principle of FLASH storage, FLASH must erase before write. GD25Q16B each sector size is 4K byte and sector is the smallest unit of erase. But when user write data to, flash ,the smallest unit is a page, the page size is 256 bytes. When you read data, you can read the entire FLASH after send reading command. Please refer to the GD25Q16B reference manual for the specific operation instructions.

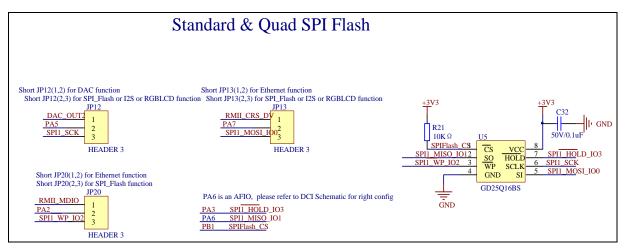

#### Hardware design

In order to read and write FLASH, we connect SPI1 pin to each SPI FLASH signal line.

Connected line is show as following:

PB1——SPIFLASH\_CS——GD25Q16B\_CS

PA5——SPI1\_CLK——GD25Q16B\_SCLK

PA7-SPI1\_MOSI\_IO0-GD25Q16B\_SI

PA6--SPI1\_MISO\_IO1--GD25Q16B\_SO

PA2——SPI1\_WP\_IO2——GD25Q16B\_WP

PA3——SPI1\_HOLD\_IO3——GD25Q16B\_HOLD

The following figure is GD32207I-EVAL-V1.0 development board Hardware connection of SPI FALSH module:

Figure 5-20 Schematic diagram of SPI

#### Software design

Based on the firmware library, according to the GD SPI FLASH datasheet, the serial FLASH driver file is added. According to the operation instructions described in the data sheet, to achieve the GD SPI FLASH ID read, erase, data read and write operations. Please refer to the GD25Q16B datasheet for specific instructions.

This Demo use quad SPI interface to read and write SPI NOR FLASH. Firstly, read the ID of SPI\_FLASH, and then erase a sector from an address, lastly, use the quad wire mode to write and read 256 bytes from the address.

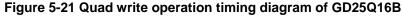

The following describes how to achieve quad wire write operation according to the clock timing of GD25Q16B datasheet:

Following is the code how to write 256 bytes to the FLASH:

```

void

QSPI_FLASH_PageWrite(uint8_t*

pBuffer,

uint32_t

WriteAddr,

uint16_t

NumByteToWrite)

{

/* Enable the FLASH Quad Mode */

QSPI_FlashQuad_Enable();

/* Enable the write access to the FLASH */

SPI_FLASH_WriteEnable();

/* Select the FLASH: Chip Select low */

SPI_FLASH_CS_LOW();

/* Send "Quad Write to Memory " instruction */

SPI_FLASH_SendByte(QUADWRITE);

/* Send WriteAddr high nibble address byte to write to */

SPI_FLASH_SendByte((WriteAddr & 0xFF0000) >> 16);

/* Send WriteAddr medium nibble address byte to write to */

```

```

SPI_FLASH_SendByte((WriteAddr & 0xFF00) >> 8);

/* Send WriteAddr low nibble address byte to write to */

SPI FLASH SendByte(WriteAddr & 0xFF);

/* Enable the QSPI */

QSPI_Enable(SPI1,ENABLE);

/* Enable the QSPI Write Operation*/

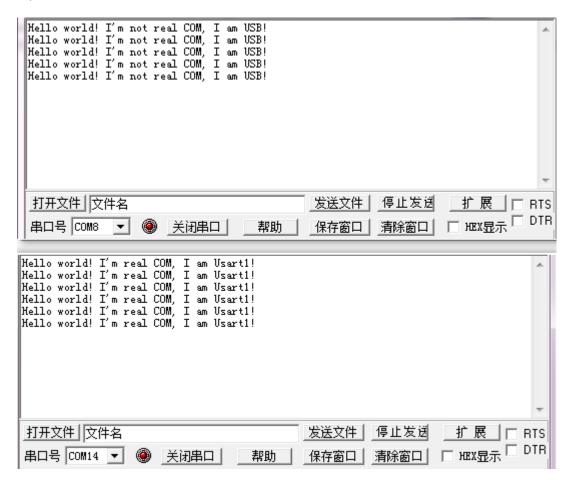

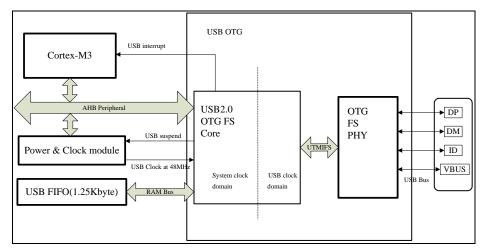

QSPI_Write_Enable(SPI1,ENABLE);

/* while there is data to be written on the FLASH */

while (NumByteToWrite--)

{

/* Send the current byte */

SPI_FLASH_SendByte(*pBuffer);

/* Point on the next byte to be written */

pBuffer++;

}

/* Deselect the FLASH: Chip Select high */

SPI_FLASH_CS_HIGH();

/* Disable the QSPI Function */

QSPI_Enable(SPI1,DISABLE);

/* Wait the end of Flash writing */

SPI_FLASH_WaitForWriteEnd();

}

```

Quad wire write operation process:

- Send command to the FLASH, use the QSPI\_FlashQuad\_Enable () function to achieve the FLASH into quad mode

- 2. Pull low chip select signal, send quad write command QUADWRITE (0x32) and following 24 bit starting address that the data wan to write in standard SPI mode

- 3 .Enable the GD32MCU SPI1 QSPI function, and set the write operation;

- 4. Until the end of the GD32MCU SPI1 transmission in the quad wire mode, and then chip

select pin driven high, close the SPI1 quad wire SPI function;

5. Achieved a page data write operation after the last data write complete.

Quad wire SPI read operation is similar to the write operation. Please refer to the GD25Qxx.c file. In addition, the read ID command, erase command, read or write register command of FLASH memory chip GD25Q16B is performed in the standard SPI mode, only user read or write data at quad SPI mode.

#### 5.8.3. **DEMO Implementation Result**

Ensure GD32207I-EVAL-V1.0 development board JP4/JP12/JP13/JP19/JP27 jumper cap jump to SPI, computer serial port line connected to the COM1 port of development board, set the baud rate of serial assistant software to 115200, 8 bits data bit, 1 bit stop bit. Download the program into the development board, through the serial assistant software can observe the operation condition, will display the ID of the flash, 256 bytes data which write to and read from flash. The following is the experimental results.

## 5.9. EXMC\_NAND Flash

#### 5.9.1. DEMO Purpose

There is a 1Gb NAND Flash (HY27UF081G2A) on the GD32207I-EVAL-V1.0 board. The NAND Flash can be accessed via EXMC module of GD32F207IKT6. This Demo is used to show how to use EXMC NAND Flash controller to access NAND Flash.

GD32F20X EXMC main features:

- Supported external memory:

- SRAM

- PSRAM/SQPI-PSRAM

- ROM

- Nor Flash

- 8-bit or 16-bit NAND Flash

- 16-bit PC Card

- Synchronous DRAM(SDRAM)

- Conversion interface between the AHB bus and the external device protocol

- Offer a variety of programmable timing parameters to meet user specific needs

- Each bank has a separate chip-select signal which can be configured independently

- Support independent configuration of reading and writing operation timing for some devices

- Provide ECC calculating hardware module for NAND Flash memory block

- Provide 8-bit or 16-bit or 32-bit data bus

- Support address and data bus multiplexing for NOR Flash and PSRAM

- For some devices, write enable signal and byte select signal can be provided

- Automatic split AHB transaction if AHB bus data size is greater than external memory data size

#### 5.9.2. **DEMO Principle**

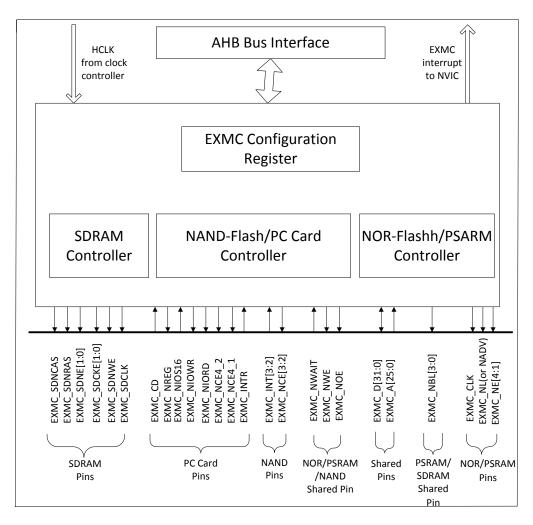

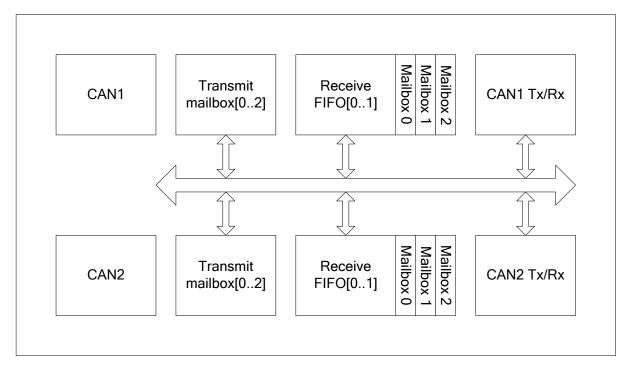

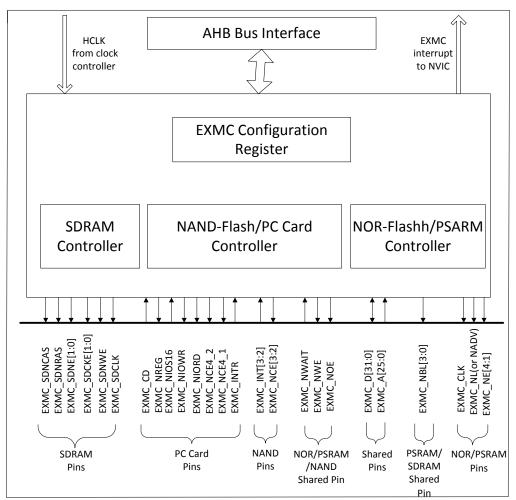

As shown below, EXMC module includes six parts: AHB bus interface, EXMC configuration registers, NOR Flash memory controller, NAND Flash and PC Card controller, SDRAM controller, external device interface. Reference clock of EXMC module is the AHB clock (HCLK).

Figure 5-22 The EXMC block diagram

NAND Flash interface:

Table 5-4 8-bit or 16-bit NAND Flash interface signal

| EXMC Pin        | Direction     | Functional description                              |  |  |

|-----------------|---------------|-----------------------------------------------------|--|--|

| A[17]           | Output        | NAND Flash address latch (ALE)                      |  |  |

| A[16]           | Output        | NAND Flash command latch (CLE)                      |  |  |

| D[7:0]/ D[15:0] | Input /Output | 8-bit multiplexed, bidirectional address/data bus   |  |  |

| D[1.0]/ D[13.0] | input/Output  | 16-bit multiplexed, bidirectional address/data bus  |  |  |

| NCE[x]          | Output        | Chip select, x = 2, 3                               |  |  |

| NOE(NRE)        | Output        | Output enable                                       |  |  |

| NWE             | Output        | Write enable                                        |  |  |

| NWAIT/INTx      | Input         | NAND Flash ready/busy input signal to the EXMC, x=2 |  |  |

EXMC provides the conversion interface between AHB bus and external device protocol. 32-bit of AHB read or write accesses can be split into several consecutive 8-bit or 16-bit read or write operations.

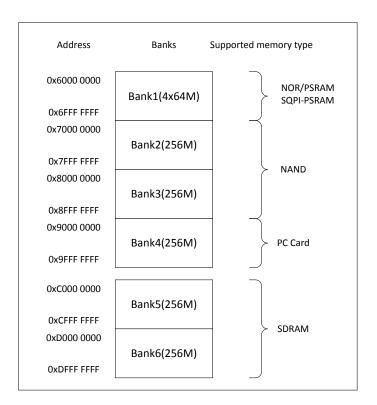

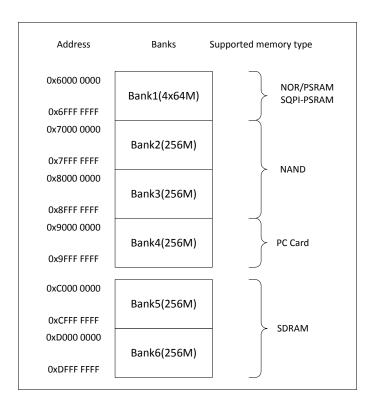

EXMC external memory can be divided into many banks and they can support different types of memory. Each bank is 256 Mbytes. The address space of each bank and the supported

memory type are shown in following figure.

Figure 5-23 EXMC memory banks

You can access NAND Flash through the Bank2 or Bank3, and EXMC module provides dedicated registers to generate the appropriate read and write timing according to user needs and the characteristics of external memory. In addition, EXMC provide ECC computing module for access NAND Flash.

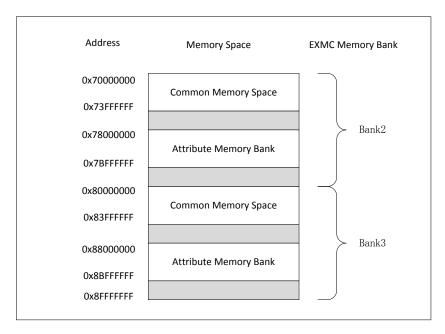

As shown below, both Bank2 and bank3 are divided into two sections, which are attribute memory space and common memory space.

Figure 5-24 NAND address mapping

For NAND Flash, common space and attribute space in the low 256K bytes of bank2 or bank3 space can be divided into three sections. The following figure is a partition diagram of bank2 common space. The attribute space of bank2, the common space and attribute space of bank3 are divided as well.

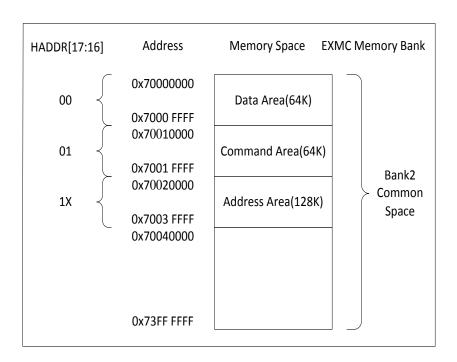

Figure 5-25 Diagram of bank2 common space

HADDR [17:16] bit are used to select one of the three area. HADDR [17:16]=00 selects the data area, HADDR[17:16]=01 selects the command area, and HADDR[17:16]=1X selects the address area. Application software uses the 3 area to access NAND Flash. Operating

rules are as follows:

- Send a command to NAND Flash memory: Software writes commands in the command area.

- 2) Specified the NAND Flash operation address: Software writes the operation address in the address area. If the number of operation address bytes is excessive, the process of writing operation address should be split into several consecutive writes in the address section.

- 3) Read or write the data to NAND Flash: The software reads or writes the data from or to NAND Flash data area. Since the NAND Flash memory will increase the operation address automatically, there is no need to increase the address of the data section manually to access consecutive memory locations.

The schematic diagram of 1Gb NAND Flash (HY27UF081G2A) which is on the GD32207I-EVAL-V1.0 board is shown in Figure 5-26. Data width of the NAND Flash is 8bit. Page size is (2K+64 spare) Bytes. Block size is 64 pages, namely, (128K + 4K spare) Bytes. The total storage space of this NAND Flash is (2K+64) x Bytes 64 x Pages 1024 Blocks. It is programmed basically by page, and the Erase operation is done on a block basis.

Figure 5-26 Schematic diagram of EXMC-NAND Flash function

According to NAND Flash access rules, it is required to send command firstly. And different NAND Flash device may have different operating commands .The command sets of HY27UF081G2A are shown below.

**Table 5-5 Command sets**

| FUNCTION           | 1st CYCLE | 2nd CYCLE | 3rd CYCLE | 4th CYCLE | Acceptable<br>command during<br>busy |

|--------------------|-----------|-----------|-----------|-----------|--------------------------------------|

| READ 1             | 00H       | 20H       | -         | -         |                                      |

| READ FOR COPY-BACK | 00H       | 35H       | -         | -         |                                      |

| READ ID            | 90H       | -         | -         | -         |                                      |

| RESET              | FFH       | -         | -         | -         | YES                                  |

| PAGE PROGRAM       | 80H       | 10H       | -         | -         |                                      |

| COPY BACK PGM      | 85H       | 10H       | -         | -         |                                      |

| BLOCK ERASE          | 60H | D0H | - | - |     |

|----------------------|-----|-----|---|---|-----|