# Au8310 High Efficiency Low Quiescent Current Buck-Boost Converter with I2C Interface

### **General Description**

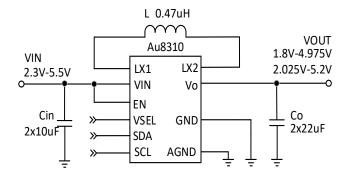

The Au8310 is a high-current, buck-boost switching converter for systems using new battery chemistries. It maintains voltage regulation while providing excellent efficiency and very low output voltage ripple when the input voltage is close to the output voltage.

The Au8310 is capable of delivering at least 2.5A continuous output current (VOUT=3.3V) across a battery voltage range of 2.5V to 4.5V. This maximizes the energy utilization of advanced, single-cell Li-ion battery chemistries that have significant capacity left at voltages below the system voltage.

The Au8310 supports a broader set of programmable features that can be accessed using an I2C interface. With a programmable output voltage range of 1.8V to 5.2V, the Au8310 is ideal for applications which require dynamically changing supply voltages. A programmable slew rate can be selected to provide smooth transitions between different output voltage settings.

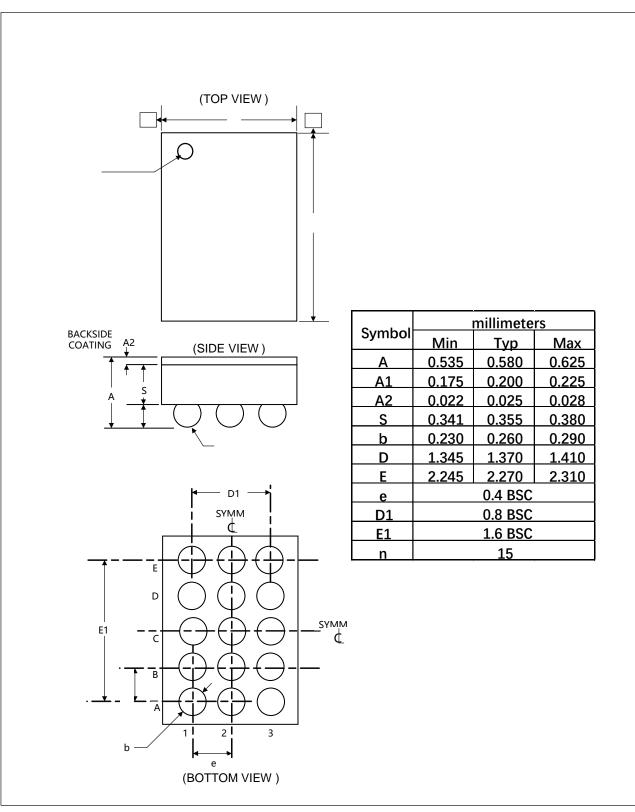

The Au8310 is available in a 15 bump, 0.4mm pitch WLCSP (1.37mmx 2.27mm) with a 2.5MHz switching frequency, which further reduces the size of external components.

### Features

- Automatic and Seamless Transition Between Buck, Buck-Boost and Boost operation.

- Maintains Steady Output Voltage at Wide Input Voltage Range from 2.3V to 5.5V.

- Output Current:

2.5A for VIN≥2.5V, VOUT=3.3V;

2.5A for VIN≥2.8V, VOUT=3.5V.

- 2.5MHz Typical Switching Frequency.

- Integrated Soft Start.

- I2C interface (Up to 1MHz).

- Programmable Output Voltage and Slew-rate with I2C interface.

- VSEL Pin to toggle between two output voltage presets.

- High Efficiency: Up to 95.5%.

- 15µA V<sub>IN</sub> Quiescent Current when ENABLE BIT=0 in CONTROL Register.

- EN pin Shutdown Function with Less Than 1µA Quiescent Current.

- Output Capacitor Discharge Function to Bleed Output.

- Over-Temperature Protection, Over-Current Protection, Short Circuit Protection and Input Voltage Protection.

- Small 1.37mmx2.27mm, 15-pin WLCSP.

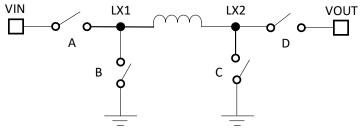

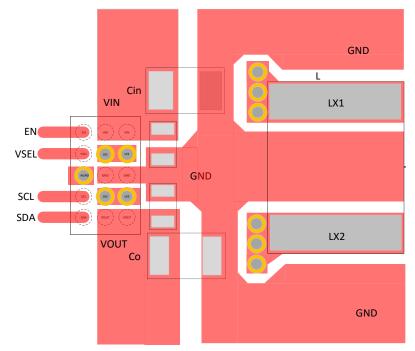

#### Figure 1 Simplified Schematic

### Application

- System Pre-Regulator (Smartphone, Tablet, EFT Terminal, Telematics)

- Point-of-Load Regulation (Wired Sensor, Port/Cable Adapter and Dongle)

- Fingerprint, Face-ID, Camera Sensors (Smartphone, Electronic Smart Lock, IP Network Camera)

- RF Amplifier Supply (Smart Sensors)

- Thermoelectric Device (TEC/TEM) Supply

- (Datacom, Optical Modules, Cooling/Heating)

### **Table of Contents**

| 1   | Pi  | in Cor      | nfiguration and Functions                          | 4  |

|-----|-----|-------------|----------------------------------------------------|----|

| 2   | S   | pecific     | cations                                            | 4  |

| 3   | T   | ypical      | Performance Curves                                 | 10 |

| 4   | D   | etaile      | d Description                                      | 12 |

| 4.  | 1   | Over        | view                                               | 12 |

| 4.2 | 2   | Fund        | tional Block Diagram                               | 12 |

| 4.3 | 3   | Feat        | ure Description                                    | 13 |

|     | 4.3 | 8.1         | Buck-Boost Conversion Topology                     | 13 |

|     | 4.3 | 8.2         | PWM Operation                                      | 13 |

|     | 4.3 | 3.3         | PFM Operation                                      | 13 |

|     | 4.3 | 8.4         | Internal Supply and References                     | 14 |

|     | 4.3 | 8.5         | Enable Input                                       | 14 |

| 4   | 4.3 | 8.6         | Soft Discharge                                     | 14 |

|     | 4.3 | 8.7         | POR Sequence and Soft-Start                        | 14 |

|     | 4.3 | 8.8         | Internal Compensation                              |    |

|     | 4.3 | 8.9         | Operation with VIN Close to VOUT                   | 14 |

| 4   | 4.3 | 8.10        | Output Voltage Selection (VSEL)                    | 15 |

| 4   | 4.3 | 3.11        | Dynamic Voltage Scaling                            | 15 |

| 4.4 | 4   | Prote       | ection Functions                                   |    |

| 4   | 4.4 | l.1         | Input Voltage Protection (IVP)                     | 16 |

| 4   | 4.4 | .2          | OverCurrent Protection                             | 17 |

| 4   | 4.4 | .3          | OverVoltage Protection                             | 17 |

| 4   | 4.4 | 1.4         | Thermal Shutdown                                   | 17 |

| 4   | 4.4 | 1.5         | Power Good                                         | 17 |

| 4   | 4.4 | .6          | Load Disconnect                                    | 17 |

| 4   | 4.4 | .7          | Output Discharge                                   | 17 |

| 4.  | 5   | Devi        | ce Functional Modes                                | 17 |

| 4.6 | 6   | 12C \$      | Serial Interface                                   | 18 |

|     | 4.6 | 6.1         | Set Power Save Mode with I2C Interface             | 18 |

|     | 4.6 | 6.2         | Set Ultrasonic Mode with I2C Interface             | 18 |

|     | 4.6 | 6.3         | Ramp-PWM Operation (RPWM)                          | 18 |

|     | 4.6 | 6.4         | Digital Slew Rate Control                          | 19 |

| 4.  | 7   | Regi        | ster Map                                           | 19 |

|     | 4.7 | <b>'</b> .1 | CONTROL Register (Address = 0x01) [Default = 0x20] | 19 |

|     | 4.7 | <b>.</b> 2  | STATUS Register (Address = 0x02) [Default = 0x00]  | 19 |

|     | 4.7 | <b>'</b> .3 | DEVID Register (Address = 0x03) [Default = 0xD0]   | 20 |

|     | 4.7 | <b>'</b> .4 | VOUT1 Register (Address = 0x04) [Default = 0x3C]   | 20 |

|     | 4.7 | <b>'</b> .5 | VOUT2 Register (Address = 0x05) [Default = 0x42]   | 20 |

| 4.8 | 8   | Prog        | ramming                                            | 21 |

|     | 4.8 | 8.1         | Serial Interface Description                       | 21 |

|     | 4.8 | 3.2         | Standard-, Fast-, Fast-Mode Plus Protocol          | 21 |

|     | 4.8 | 3.3         | I2C Update Sequence                                | 23 |

| 5   | A   | pplica      | tion and Implementation                            | 23 |

| 5.  | 1   | Appl        | ication Information                                | 24 |

| 5.2 | 2   | Турі        | cal Application                                    | 24 |

| 5.3 | 3   | Indu        | ctor Selection                                     | 24 |

|     |     |             |                                                    |    |

| 5.4 | 4 VIN and VOUT Capacitor Selection | 25  |

|-----|------------------------------------|-----|

|     | Layout                             |     |

|     | 1 Layout Guidelines                |     |

|     | 2 Layout Example                   |     |

|     | Package Outline Drawing            |     |

|     | Revision History                   |     |

|     | Trademarks                         |     |

| •   |                                    | ••• |

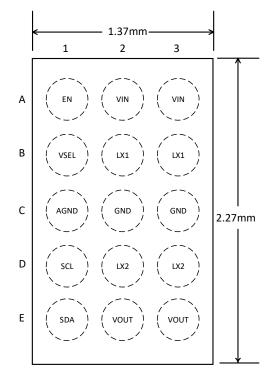

# 1 Pin Configuration and Functions

Figure 2 15-Pin WLCSP Package Top View

| Table | 1 | Pin | Fun | ctions |

|-------|---|-----|-----|--------|

|       |   |     |     |        |

| Pin number | PIN Name | I/O | Description                                                                                                                                                                                                                                                                |

|------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | EN       | I   | Enable pin. Set high to enable the device and set low to disable the device. It must not be left floating.                                                                                                                                                                 |

| B1         | VSEL     | I   | This pin selects which VOUT register is active. When a low logic level is applied to this pin, the VOUT1 register sets the output voltage. When a high logic level is applied to this pin, the VOUT2 register sets the output voltage. This pin must not be left floating. |

| C2, C3     | GND      | -   | Power Ground.                                                                                                                                                                                                                                                              |

| B2, B3     | LX1      | -   | The Switching node pin of the buck side.                                                                                                                                                                                                                                   |

| D2, D3     | LX2      | -   | The Switching node pin of the boost side.                                                                                                                                                                                                                                  |

| A2, A3     | VIN      | -   | Power supply for the power stage.                                                                                                                                                                                                                                          |

| E2, E3     | VOUT     | -   | Buck-boost converter output.                                                                                                                                                                                                                                               |

| C1         | AGND     | -   | Analog Ground.                                                                                                                                                                                                                                                             |

| D1         | SCL      | I/O | I2C serial interface clock. Pull this pin up to the I2C bus voltage with a resistor or a current source.                                                                                                                                                                   |

| E1         | SDA      | I/O | I2C serial interface data. Pull this pin up to the I2C bus voltage with a resistor or a current source.                                                                                                                                                                    |

# 2 Specifications

#### Table 2 Absolute Maximum Ratings

Over operation junction temperature range (unless otherwise noted)<sup>(1)</sup>

| Symbol           | Parameter                                                          | Min  | Тур | Max | Units |

|------------------|--------------------------------------------------------------------|------|-----|-----|-------|

| Vı               | Input Voltage<br>(VIN,LX1,LX2,VOUT,EN,VSEL,SDA,SCL) <sup>(2)</sup> | -0.3 |     | 6   | V     |

| TOPR             | Operating junction temperature                                     | -40  |     | 150 | °C    |

| T <sub>STG</sub> | Storage temperature                                                | -65  |     | 150 | °C    |

Notes:

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Expose to absolute maximum rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal, unless otherwise noted.

#### **Table 3 Recommended Operation conditions**

Over operating free-air temperature range (unless otherwise noted)

| Symbol                                       | Parameter                                     | Min   | Тур  | Max   | Units |

|----------------------------------------------|-----------------------------------------------|-------|------|-------|-------|

| Vin                                          | Input Voltage                                 | 2.3   |      | 5.5   | V     |

|                                              | Output Voltage (High range)                   | 2.025 |      | 5.200 | V     |

| Vout                                         | Output Voltage (Low range)                    | 1.800 |      | 4.975 | v     |

| SCL,SDA,VSEL                                 | High-level input voltage                      | 1.3   |      | Vin   | V     |

| SCL,SDA,VSEL                                 | Low-level input voltage                       | 0     |      | 0.3   | V     |

| EN                                           | EN input voltage                              | 0     |      | Vin   | V     |

| V <sub>OUT</sub> =3.3V,V <sub>IN</sub> ≥2.5V |                                               |       |      | 2.5   |       |

| V <sub>OUT</sub> =3.5V,V <sub>IN</sub> ≥2.5V |                                               |       |      | 2     |       |

| V <sub>OUT</sub> =3.5V,V <sub>IN</sub> ≥2.8V | Output current <sup>(1)</sup>                 |       |      | 2.5   | A     |

| $V_{OUT}=3.3V, V_{IN}\geq 3V$                |                                               |       |      | 3     |       |

| Cin <sup>(2)</sup>                           | Input capacitance                             | 5     |      |       | μF    |

| Co <sup>(2)</sup>                            | Output capacitance                            | 13    | 16   |       | μF    |

| L                                            | Inductance                                    | 0.39  | 0.47 | 0.56  | μH    |

| TJ                                           | Operating junction temperature range          | -40   |      | 125   | °C    |

| T <sub>A</sub>                               | Operating free-air junction temperature range | -40   |      | 85    | °C    |

Notes:

(1) The device can sustain the maximum recommended output current only for short durations before its junction temperature gets too hot. Users must verify that the thermal performance of the end application can support the maximum output current.

#### **Table 4 ESD Ratings**

| Symbol             | Parameter     | Condition                                                                             | Value | Units |

|--------------------|---------------|---------------------------------------------------------------------------------------|-------|-------|

| V <sub>(ESD)</sub> | Electrostatic | Human-body model (HBM),<br>per ANSI/ESDA/JEDEC JS-<br>001 <sup>(1)</sup>              | ±2000 | V     |

| V (ESD)            | Discharge     | Charged-device model (CDM),<br>per JEDEC specification<br>JESD22- C101 <sup>(2)</sup> | ±500  | V     |

#### Notes:

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process

.

<sup>(2)</sup> Effective capacitance after DC bias effects have been considered.

#### **Table 5 Thermal Characteristics**

| Symbol  | THERMAL METRIC                            | Value | Units |

|---------|-------------------------------------------|-------|-------|

| Reja    | Junction-to-ambient thermal resistance    | TBD   | °C/W  |

| RejCtop | Junction-to-case (top) thermal resistance | TBD   | °C/W  |

| Rөjb    | Junction-to-board thermal resistance      | TBD   | °C/W  |

Notes: Power rating at a specific ambient temperature TA should be determined with a junction temperature of 125 °C. Thermal management of PCB should strive to keep the junction temperature at or below 125 °C for best performance and long-term reliability.

#### **Table 6 Electrical Characteristics**

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted). Typical values are at VIN=3.6V, VouT=3.3V and T<sub>J</sub> =  $25^{\circ}C$  (unless otherwise noted).

| Symbol              | Parameter                               | Condition                                                                                    | Min  | Тур   | Max  | Units |

|---------------------|-----------------------------------------|----------------------------------------------------------------------------------------------|------|-------|------|-------|

| Supply              |                                         | I                                                                                            |      |       |      |       |

| Vin                 | Supply Voltage (Vin<br>Pin)             | Vin                                                                                          | 2.3  |       | 5.5  | V     |

| Vin(UVLO)           | VIN internal UVLO                       | V <sub>IN</sub> rising                                                                       | 2.1  | 2.2   | 2.3  | V     |

| Vin(HYS)            | threshold and<br>hysteresis             | UVLO threshold voltage<br>hysteresis                                                         |      | 150   |      | mV    |

| Isd                 | V <sub>IN</sub> shutdown supply current | EN=0V, V <sub>IN</sub> =3.6V,<br>Vo=0V,TJ=25°C                                               |      | 0.35  |      | μA    |

| lα                  |                                         | EN=3.6V, VI№=3.6V,<br>Io=0A (none switching),<br>Vo=3.3V,TJ=25°C                             |      | 33    |      | μA    |

| la                  | V <sub>IN</sub> operating current       | EN=3.6V, VIN=3.6V,<br>Output disabled by<br>ENABLE bit in Control<br>Register, Vo=0V,TJ=25°C |      | 15    |      | μΑ    |

| Logic Signals       | 3                                       |                                                                                              | 1    |       |      |       |

| V <sub>IH(EN)</sub> |                                         | Rising                                                                                       | 1.07 | 1.10  | 1.13 | V     |

| V <sub>IL(EN)</sub> | Enable threshold                        | Falling                                                                                      | 0.97 | 1.00  | 1.03 | V     |

| VEN(HYS)            |                                         | EN Hysteresis voltage                                                                        | 40   | 100   |      | mV    |

| Vih                 | VSEL/SCL/S DA                           | Rising                                                                                       |      |       | 1.2  | V     |

| VIL                 | threshold                               | Falling                                                                                      | 0.4  |       |      | V     |

| Іін                 | High-level input<br>current             | VSEL=SDA=SCL=1.8V,<br>no pullup resistor                                                     |      | ±0.01 | ±0.1 |       |

| IIL                 | Low-level input current                 | VSEL=SDA=SCL=0V, no pullup resistor                                                          |      | ±0.01 | ±0.1 | μΑ    |

| Isl                 | Low-level sink current                  | SDA=0.4 V                                                                                    | 20   |       |      | mA    |

| lів                 | EN pin Input bias current               | EN=0V to 5.5V                                                                                |      | ±0.01 | ±0.1 | μA    |

| MOSFET              | - <b>·</b>                              |                                                                                              |      | 1     | 1    | 1     |

| Rds_Hs_<br>buck     | High-side switch resistance             | VIN=3V,Vout=3.3 V,<br>Io=200mA                                                               |      | 38    |      | mΩ    |

| Rds_Ls_<br>buck     | Low-side switch resistance [1]          | Vin=3V,Vout=3.3V,<br>Io=200mA                                                                |      | 15    |      | mΩ    |

| Rds_Hs_<br>boost                        | High-side switch resistance              | VIN=3V,Vout=3.3V,<br>Io=200mA                                 |       | 45   |       | mΩ    |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|-------|------|-------|-------|

| Rds_Ls_<br>boost                        | Low-side switch resistance [1]           | VIN=3V,Vout=3.3V,<br>Io=200mA                                 |       | 12   |       | mΩ    |

| Output Voltage                          | e Regulation                             |                                                               | •     |      |       | •     |

|                                         | Vout Range                               | High Range                                                    | 2.025 |      | 5.200 | V     |

|                                         |                                          | Low Range                                                     | 1.800 |      | 4.975 | V     |

|                                         |                                          | PWM Mode                                                      | -1.5  |      | 1.5   | %     |

|                                         | Vout Accuracy                            | PFM Mode                                                      | -1.5  |      | 3.5   | %     |

| M                                       | Vou⊤ default output<br>voltage (RANGE=0) | VSEL=Low                                                      |       | 3.30 |       | V     |

| V <sub>OUT</sub>                        |                                          | VSEL=High                                                     |       | 3.45 |       | V     |

| ΔVουτ / ΔΙουτ                           | Load Regulation<br>(PWM)                 | VIN =3.6V, V <sub>OUT</sub> =3.3V,<br>Io step from 0.2A to 2A |       | 5    |       | μV/mA |

| ΔVουτ/ ΔΙουτ                            | Load Regulation<br>(PFM)                 | VIN=3.6V,Vout=3.3V,<br>Io step from 0A to 0.2A                |       | 400  |       | μV/mA |

| ΔV <sub>OUT</sub> /<br>ΔVin             | Line Regulation<br>(PWM)                 | Vout=3.3V,Io=1A,VIN<br>sweep from 2.5V to 5.5V                |       | 5    |       | mV/V  |

| ΔV <sub>OUT</sub> /<br>ΔV <sub>IN</sub> | Line Regulation<br>(PFM)                 | Vout=3.3V,Io=0.2A,VIN<br>sweep from 2.5V to 5.5V              |       | 12.5 |       | mV/V  |

[1] Measured at Pins.

#### Table 7 Electrical Characteristics (Continued)

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted). Typical values are at VIN=3.6V, Vout=3.3V and TJ =  $25^{\circ}$ C (unless otherwise noted).

| Symbol                 | Parameter                   | Condition                           | Min | Тур     | Max | Units    |

|------------------------|-----------------------------|-------------------------------------|-----|---------|-----|----------|

| Current Limit          | t                           |                                     |     |         |     |          |

| I <sub>LIM_boost</sub> | High-side switch            | VIN=2.9V, VOUT=3.6V                 | 5.2 | 5.85    | 6.5 | А        |

| I <sub>LIM_buck</sub>  | current limit threshold     | VIN=5V, VOUT=3.3V                   | 3.8 | 4.5     | 5.2 | А        |

| Power Good             |                             |                                     |     |         |     | <u>.</u> |

| VR(PG)                 | Power-good threshold        | Rising threshold                    |     | 95%Vout |     | V        |

| VF(PG)                 |                             | Falling threshold                   |     | 90%Vout |     | v        |

| td(PG)                 | Power-good delay            | Vout falling                        |     | 50      |     | μs       |

| IVP                    |                             |                                     |     |         |     | -        |

| IVP(VTH)               | VIN OVP rising<br>threshold | Vin increases                       |     | 5.7     |     | V        |

| IVP(HYS)               | VIN OVP hysteresis          | Vin decreases                       |     | 100     |     | mV       |

| Thermal Shu            | itdown                      |                                     |     |         |     |          |

| Tas                    | Thermal shutdown            | Shutdown,<br>temperature increasing |     | 150     |     | °C       |

| T <sub>SD</sub>        | Thermal shutdown hysteresis | Reset, temperature decreasing       |     | 20      |     | °C       |

| Switching Fr           | equency                     |                                     |     |         |     |          |

| f <sub>sw</sub>        | Switching Frequency         | CCM Mode                            | 2.1 | 2.5     | 2.9 | MHz      |

| I2C Interface          | )                           |                                     |     |         |     |          |

| Address                | Device I2C Address          | 7-bit slave address                 |     | 0x75    |     |          |

| Soft-Start an          | d Soft Discharge            | •                                   |     | •       |     |          |

| Symbol            | Parameter                               | Condition                                                                                                                     | Min | Тур  | Max | Units |

|-------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| td(EN)            |                                         | Delay between a rising<br>edge on the EN pin<br>and the start of the<br>output<br>voltage ramp.TJ=25°C,<br>VIN=3.6V           |     | 320  |     | μs    |

| Vou⊤_rise<br>time | Soft-start and Soft discharge           | Time from when VOUT<br>starts rising to VOUT<br>reaches 95% target<br>voltage. Buck mode.<br>VIN=3.6V,VOUT=3.3V,<br>Io=100mA. |     | 110  |     | μs    |

| I_dis             |                                         | Vou⊤ discharge<br>current,Vin=3.6V,Vou⊤<br>≥0.8V                                                                              | 50  |      |     | mA    |

| PFM/PWM Tr        | ansient                                 |                                                                                                                               |     |      |     |       |

|                   | Load Current<br>Threshold PFM to<br>PWM | VIN=3.6V,Vout=3.3V                                                                                                            |     | 750  |     |       |

|                   | Load Current<br>Threshold PWM to<br>PFM | VIN=3.6V,Vout=3.3V                                                                                                            |     | 250  |     | mA    |

| OVP               |                                         |                                                                                                                               |     |      | •   | •     |

| Vout_ov_r         | Vout Over Voltage                       | VIN=3.6V, VOUT=3.3V,<br>OVP Rising Threshold                                                                                  |     | 5.82 |     | V     |

| Vout_ov_f         | Protection Threshold                    | VIN=3.6V, VOUT=3.3V,<br>OVP Falling Threshold                                                                                 |     | 5.65 |     | V     |

### **Table 8 Timing Requirements**

#### Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

| Symbol              | Parameter                       | Condition      | Min  | Тур | Max  | Units |  |  |

|---------------------|---------------------------------|----------------|------|-----|------|-------|--|--|

|                     |                                 | Stand mode     | 0    |     | 100  |       |  |  |

| fscl                | SCL clock frequency             | Fast Mode      | 0    |     | 400  | kHz   |  |  |

|                     |                                 | Fast mode plus | 0    |     | 1000 |       |  |  |

|                     |                                 | Stand mode     | 4.7  |     |      |       |  |  |

| t <sub>LOW</sub>    | Low period of the SCL<br>clock  | Fast Mode      | 1.3  |     |      | μs    |  |  |

| CIOCK               | Fast mode plus                  | 0.5            |      |     |      |       |  |  |

|                     |                                 | Stand mode     | 4.0  |     |      |       |  |  |

| THICH               | High period of the SCL<br>clock | Fast Mode      | 0.6  |     |      | μs    |  |  |

|                     | CIOCK                           | Fast mode plus | 0.26 |     |      |       |  |  |

|                     | Bus free time between           | Stand mode     | 4.7  |     |      |       |  |  |

| <b>t</b> BUF        | a STOP and a START              | Fast Mode      | 1.3  |     |      | μs    |  |  |

|                     | condition                       | Fast mode plus | 0.5  |     |      |       |  |  |

|                     | Set-up time for a               | Stand mode     | 4.7  |     |      |       |  |  |

| t <sub>SU;STA</sub> | repeated START                  | Fast Mode      | 0.6  |     |      | μs    |  |  |

|                     | condition                       | Fast mode plus | 0.26 |     |      |       |  |  |

| t                   | Hold time (repeated)            | Stand mode     | 4.0  |     |      |       |  |  |

| <b>t</b> hd;sta     | START condition                 | Fast Mode      | 0.6  |     |      | μs    |  |  |

| Symbol                      | Parameter                                | Condition      | Min        | Тур | Max  | Units |

|-----------------------------|------------------------------------------|----------------|------------|-----|------|-------|

|                             |                                          | Fast mode plus | 0.24       |     |      |       |

|                             |                                          | Stand mode     | 250        |     |      |       |

| tsu;dat                     | Data set-up time                         | Fast Mode      | 100        |     |      | ns    |

|                             |                                          | Fast mode plus | 50         |     |      |       |

|                             |                                          | Stand mode     | 0          |     |      |       |

| t <sub>HD;DAT</sub>         | Data hold time                           | Fast Mode      | 0          |     |      | μs    |

|                             |                                          | Fast mode plus | 0          |     |      |       |

|                             |                                          | Stand mode     |            |     | 1000 |       |

| tr                          | Rise time of both SDA<br>and SCL signals | Fast Mode      | 20         |     | 300  | ns    |

|                             |                                          | Fast mode plus |            |     | 120  |       |

|                             |                                          | Stand mode     |            |     | 300  |       |

| tr Fall time of and SCL sig | Fall time of both SDA                    | Fast Mode      | 20xVpd/5.5 |     | 300  | ns    |

|                             | and OOL signals                          | Fast mode plus | 20xVpd/5.5 |     | 120  |       |

|                             |                                          | Stand mode     | 4          |     |      |       |

| tsu;sto                     | Set-up time for STOP<br>condition        | Fast Mode      | 0.6        |     |      | μs    |

|                             | Condition                                | Fast mode plus | 0.26       |     |      |       |

|                             |                                          | Stand mode     |            |     | 3.45 |       |

| t <sub>VD;DAT</sub>         | Data valid time                          | Fast Mode      |            |     | 0.9  | μs    |

|                             |                                          | Fast mode plus |            |     | 0.45 |       |

|                             |                                          | Stand mode     |            |     | 3.45 |       |

| tvd;ack                     | Data valid acknowledge time              | Fast Mode      |            |     | 0.9  | μs    |

|                             |                                          | Fast mode plus |            |     | 0.45 |       |

|                             |                                          | Stand mode     |            |     | 400  |       |

| Cb                          | Capacitive load for<br>each bus line     | Fast Mode      |            |     | 400  | pF    |

|                             |                                          | Fast mode plus |            |     | 550  |       |

#### Table 9 Switching Characteristics

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted). Typical values are at VIN=3.6V, Vout=3.3V and TJ =  $25^{\circ}$ C (unless otherwise noted).

| Symbol   | Parameter                                                             | Condition                                                 | Min | Тру  | Max | Units |

|----------|-----------------------------------------------------------------------|-----------------------------------------------------------|-----|------|-----|-------|

|          |                                                                       | SLEW=00b, forced-<br>PWM operation ±1V/ms                 |     | ±1   |     |       |

| SR       | SR Slew rate of internal<br>ramp during<br>dynamic voltage<br>scaling | SLEW=01b, forced-<br>PWM operation<br>±2.5V/ms            |     | ±2.5 |     | V/ms  |

|          |                                                                       | SLEW=10b, forced-<br>PWM operation ±5V/ms                 |     | ±5   |     |       |

|          |                                                                       | SLEW=11b, forced-<br>PWM operation ±10V/ms                |     | ±10  |     |       |

| td(VSEL) | Delay between<br>rising edge of VSEL<br>and start of DVS<br>ramp      | Measured from rising<br>edge of VSEL to start of<br>ramp. |     |      | 5   | μs    |

| tw(VSEL) | VSEL pulse<br>duration                                                | VSEL = high or low                                        | 5   |      |     | μs    |

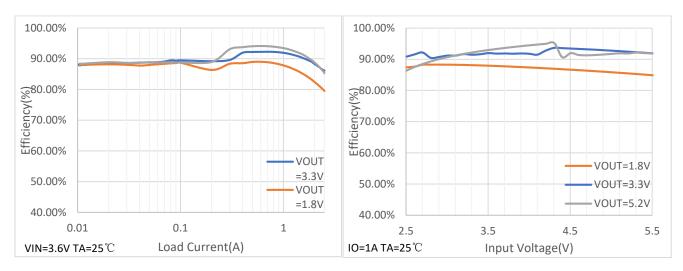

## **3** Typical Performance Curves

Table10 lists the components that were used for the measurement waveforms contained in the following pages.

| Reference | Description                         | Part Number       | Manufacture                           |

|-----------|-------------------------------------|-------------------|---------------------------------------|

| Cin       | Capacitor, 10µF,10V, 0603, Ceramic  | GRM188R61A106ME69 | Murata                                |

| Со        | Capacitor, 22µF, 10V, 0603, Ceramic | GRM187R61A226ME15 | Murata                                |

| L1        | Inductor, 0.47µH                    | XFL4015-471MEC    | Coilcraft                             |

| U1        | Integrated circuit                  | Au8310            | Ningbo Aura Semiconductor<br>Co.,Ltd. |

Figure 3 Efficiency versus Output Current

#### Figure 4 Efficiency versus Input Voltage

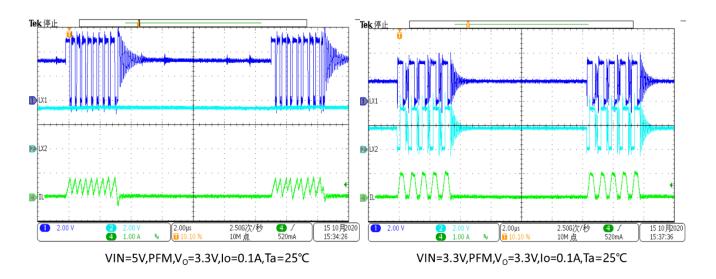

Figure 6 PFM Switching Waveforms

(Buck-Boost Operation)

### 4 Detailed Description

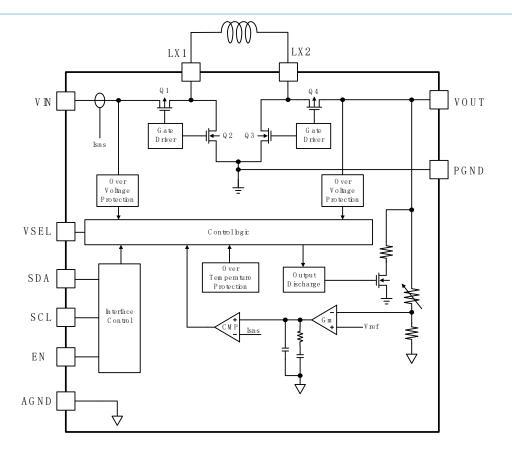

### 4.1 Overview

The Au8310 device is synchronous buck-boost converter with two integrated P-channel MOSFETs and two integrated N-channel MOSFETs. This enables the device to keep high efficiency over the complete input voltage and output voltage range. To regulate the output voltage at all possible input voltage condition, the device automatically switches from buck operation to boost operation and back as required by the configuration. The

device operates as a buck converter when V<sub>IN</sub> > V<sub>OUT</sub>, and as a boost converter when V<sub>IN</sub> < V<sub>OUT</sub>. When V<sub>IN</sub> ≈ V<sub>OUT</sub>,

the device operates in buck-boost mode. The device provides a seamless transition between buck and boost operation. There is no mode of operation in which all 4 switches are switching at the same time. The RMS current through the switches and the inductor is kept at a minimum, to minimize switching and conduction losses. Controlling the switches this way allows the converter to always keep higher efficiency. The device provides a seamless transition between buck and boost operation.

### 4.2 Functional Block Diagram

Figure 17 Block diagram

### 4.3 Feature Description

### 4.3.1 Buck-Boost Conversion Topology

The Au8310 operates in either Buck or Boost mode. When operating in conditions where  $V_{IN}$  is close to  $V_{OUT}$ , the Au8310 alternates between Buck and Boost mode as necessary to provide a regulated output voltage.

Figure 18 Buck-Boost Topology

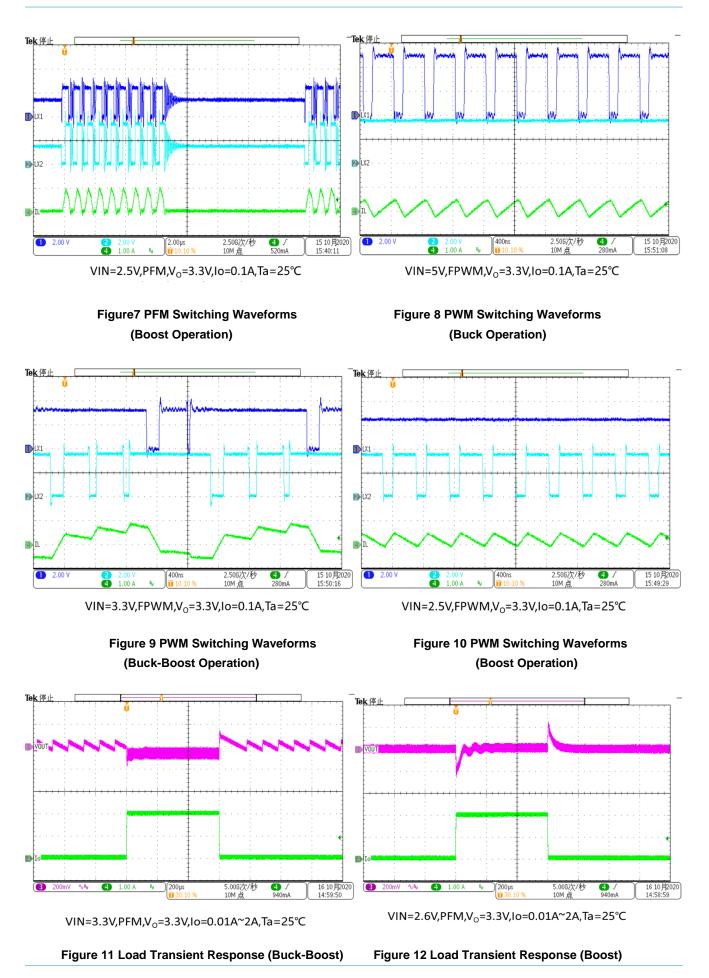

#### 4.3.2 PWM Operation

In Buck PWM mode, Switch D is continuously ON and Switch C is continuously OFF. Switches A and B operate as a synchronous buck converter when in this mode.

In Boost PWM mode, Switch A remains ON and Switch B remains OFF. Switches C and D operate as a synchronous boost converter when in this mode.

### 4.3.3 **PFM Operation**

During PFM operation in Buck mode, Switch D is continuously ON, and Switch C is continuously OFF. Switches A and B operate in Discontinuous mode during PFM operation. During PFM operation in Boost and Buck-Boost mode, the Au8310 closes Switch A and Switch C to ramp up the current in the inductor. When the inductor current reaches a certain threshold, the device turns off Switches C and turn on Switch D, so it works at bypass mode.

After a fixed time, the chip turns on Switches B and D. With Switches B and D ON, output voltage increases as the inductor current ramps down. In most operating conditions, there will be multiple PFM pulses to charge up the output capacitor. These pulses continue until  $V_{OUT}$  has achieved the upper threshold of the PFM hysteretic controller. Switching then stops and remains stopped until  $V_{OUT}$  decays to the lower threshold of the hysteretic PFM controller.

#### 4.3.4 Internal Supply and References

Referring to the "Block Diagram" in Figure 17, the Au8310 provides two power input pins. The VIN pin not only supplies input power to the DC/DC converter, but also provides an operating voltage source required for stable VREF generation. Separate ground pins (AGND and GND) are provided to avoid problems caused by ground shift due to the high switching currents.

### 4.3.5 Enable Input

The device uses a precise EN pin and is enabled by asserting the EN pin High. When the voltage applied on EN is over the rising threshold, it starts to work. Driving EN below falling threshold invokes a power-down mode in which most internal device functions are disabled.

You can also use the ENABLE bit in the Control register to enable and disable the output of the converter (see the Register Map).

| ENABLE PIN (EN) | ENABLE BIT | DEVICE STATE                 | OUTPUT STATE            |

|-----------------|------------|------------------------------|-------------------------|

| 0               | Х          | Device in Shutdown           | Output Discharge Active |

| 1               | 0          | Programming Interface Active | Output Discharge Active |

| 1               | 1          | Device Active                | Output Enabled          |

#### Table 11 Device Enable Truth Table

#### 4.3.6 Soft Discharge

When the device is disabled by driving EN LOW or ENABLE bit is set to 0, an internal NMOS switch between V<sub>OUT</sub> and GND is activated to slowly discharge the output capacitor.

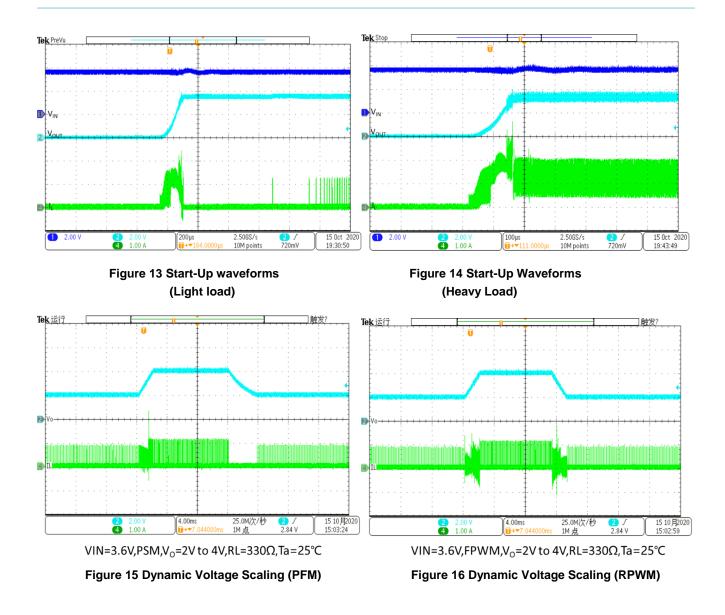

#### 4.3.7 POR Sequence and Soft-Start

Asserting the EN pin HIGH allows the device to power up. The following events occur during the start-up sequence. The internal voltage reference powers up and stabilizes. The device then starts operating.

To minimize inrush current and output voltage overshoot during start-up, the device features a controlled soft start-up. After the device is enabled, the device starts all internal reference and control circuits within the enable delay time.

The soft start feature minimizes output voltage overshoot and input inrush currents. During soft-start, the reference voltage is ramped to provide a ramping VOUT voltage. While the output voltage is lower than approximately 25% of the target output voltage, switching frequency is reduced to a fraction of the normal switching frequency which is around 1MHz to aid in producing low duty cycles necessary to avoid input inrush current spikes. Once the output exceeds 25% of the target voltage, switching frequency is increased to its nominal value.

#### 4.3.8 Internal Compensation

The buck-boost converter utilizes a proprietary internal compensation scheme to simultaneously simplify external component selection and optimize transient performance over its full operating range. No compensation design is required.

#### 4.3.9 Operation with VIN Close to VOUT

When the output voltage is close to the input voltage, the Au8310 rapidly and smoothly switches between Boost and Buck mode as needed to maintain the regulated output voltage. This behavior provides excellent efficiency and very low output voltage ripple.

### 4.3.10 Output Voltage Selection (VSEL)

The device can generate output voltages from 1.8V to 5.2V with a resolution of 25 mV. To set the output voltage range, you must first program the RANGE bit in the Control register to select the output voltage range:

- When RANGE=0, you can program the output voltage from 1.800V to 4.975V.

- When RANGE=1, you can program the output voltage from 2.025V to 5.200V.

To set the output voltage, you must also first set VSEL pin by pulling this pin High or LOW to select the output voltage register:

- When VSEL PIN=HIGH, VOUT[6:0]=VOUT2[6:0]

- When VSEL PIN=LOW, VOUT[6:0]=VOUT1[6:0]

When you have selected the output voltage range, you can program the VOUT1 register and VOUT2 register to set the output voltage:

- When RANGE=0, Vout=(VOUT[6:0]×0.025)+1.800V

- When RANGE=1, VOUT=(VOUT[6:0]×0.025)+2.025V

#### Note

To prevent output voltage transients, Ningbo Aura semiconductor recommends that you do not change the output voltage range while the converter is in operation. Instead, clear the ENABLE bit in the Control register to 0 to disable the DC/DC converter before you change the RANGE bit.

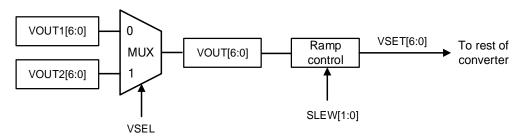

#### 4.3.11 Dynamic Voltage Scaling

The device has a dynamic voltage scaling (DVS) function which lets you change the output voltage in a controlled way during operation. Figure 19 shows a simplified block diagram of the DVS function. The VSEL pin controls a multiplexer which selects either the VOUT1 register or the VOUT2 register to control the set voltage. The ramp control block detects when the target output voltage is different from the actual output voltage and ramps the output voltage to the target voltage in 25mV steps.

You can use the 2-bit SLEW parameter in the Control register to select one of four slew rates from 1 V/ms to 10 V/ms. The device starts a DVS ramp when you change the logic level on the VSEL pin or program to a new value in the active VOUT register.

Figure 19 Dynamic Voltage Scaling Block Diagram

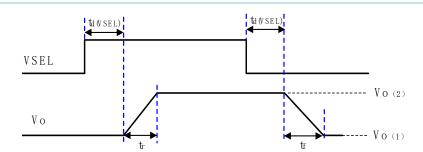

Note that if you change the contents of the active VOUT register or change the state of the VSEL pin during start-up (that is, before the end of the soft start), the converter uses the new value immediately and does not ramp gradually to the final value. Figure 20 shows the timing diagram when you use the VSEL pin to change between the output voltage values in the VOUT1 and VOUT2 registers.

Figure 20 DVS Timing Diagram Using the VSEL Pin

$$t_r = t_f = \frac{|V_o(2) - V_o(1)|}{SR}$$

Where:

$V_o(1)$  is the output voltage set by the VOUT1 register.

$V_o(2)$  is the output voltage set by the VOUT2 register.

SR is the slew rate set by the SLEW bits in the CONTROL register.

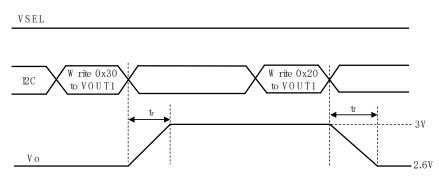

Figure 21 shows the timing diagram when you use the I2C interface to change the output voltage value in one of the VOUT registers.

Figure 21 DVS Timing Using the I2C Interface

$$t_r = t_f = \frac{|3.0 - 2.6|}{SR}$$

Where SR is the slew rate set by the SLEW bits in the CONTROL register.

### **4.4 Protection Functions**

### 4.4.1 Input Voltage Protection (IVP)

Under certain operating conditions, current can flow from the output of the device to the input. For example, this can occur during dynamic voltage scaling when the output ramps down to a lower voltage and the VOUT pin sinks current from the output capacitor. Under such conditions, if the voltage input source supplying the device cannot sink current, the voltage on the VIN pin can rise uncontrollably. Under force PWM operation (FPWM=1) and in order to make sure the input voltage stays within the permitted range, the device will enter Auto PFM mode if the voltage on the VIN pin is greater than 5.7V. The device automatically starts to switch and back to force PWM operation again when the voltage on the VIN pin is less than 5.6V.

The device sets the  $\overline{PG}$  bit in the Status register when an input overvoltage event occurs. The device clears the  $\overline{PG}$  bit if the Status register is read when the power-not-good condition no longer exists.

#### 4.4.2 OverCurrent Protection

The device has a clamp circuit which limits the peak inductor current in the event of an overload. The exact value of the output current during an overload changes with the operating conditions (V<sub>IN</sub> and V<sub>OUT</sub>) and the switching mode (buck, buck-boost, or boost). If hiccup mode is enabled, when over current is detected and the counter inside reaches 16 within 64 switching periods, it enters hiccup mode. It re-start again after 16384 switching periods time expired.

Overloads increase the power dissipation in the device, which increases its temperature. If the device becomes too hot, the thermal shutdown function turns off the converter. When the device cools down, the thermal shutdown function automatically turns on the converter again. Thus, under a permanent overload condition, the device can periodically turn on and off, as it cools down and then heats up.

#### 4.4.3 OverVoltage Protection

The device has the over-voltage protection function to avoid the output voltage exceeding critical values. When Vout hits the output OVP rising threshold, it enters HiZ mode, all the switches stop switching. It recovers from OVP when Vout drops below falling threshold.

#### 4.4.4 Thermal Shutdown

A built-in thermal protection feature protects the Au8310 if the die temperature reaches 150°C (typical). At this die temperature, the regulator is completely shut down. The die temperature continues to be monitored in this thermal shutdown mode. When the die temperature falls to 130°C (typical), the device resumes normal operation. When exiting thermal shutdown, the Au8310 executes its soft-start sequence.

When the device detects an over temperature condition, it sets the TSD bit in the Status register to 1. The device clears the TSD bit to 0 if you read the Status register when the junction temperature of the device is less than 130°C.

#### 4.4.5 Power Good

The device has a power-good function which indicates if the output of the DC/DC converter is in regulation or not. The device detects a power-good condition when the output voltage is greater than 95% of its nominal value and detects a power-not-good condition when the output voltage is less than 90% of its nominal value.

When a power-not-good condition occurs, the device sets the  $\overline{PG}$  bit in the Status register to 1. The device clears the  $\overline{PG}$  bit to 0 if you read the Status register when a power-good condition exists.

#### 4.4.6 Load Disconnect

During device shutdown, the input is disconnected from the output. This prevents any current flow from the output to the input or from the input to the output.

#### 4.4.7 Output Discharge

The device actively discharges the output when the EN pin is low or ENABLE bit=0 or VIN pin voltage is lower than UVLO threshold.

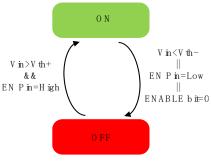

#### 4.5 Device Functional Modes

The device has two functional modes: off and on. The device enters the on mode when the voltage on the VIN pin is higher than the UVLO threshold and a high logic level is applied to the EN pin. The device enters the off mode when the voltage on the VIN pin is lower than the UVLO threshold or a low logic level is applied to the EN pin.

**Figure 22 Device Functional Modes**

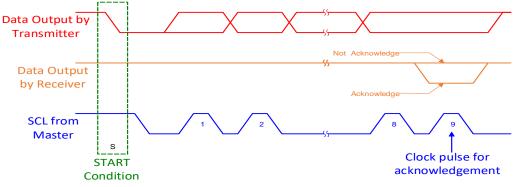

### 4.6 I2C Serial Interface

The Au8310 supports a bidirectional bus-oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter and the receiving device as the receiver. The device controlling the transfer is the master and the device being controlled is the slave. The master always initiates data transfers and provides the clock for both transmit and receive operations. Therefore, the Au8310 operates as a slave device in all applications. The SCL and SDA pin need external pull-up resistor connected with a proper voltage level. Pull the SCL and SDA pins to a proper voltage level if the I2Cinterface is not used. All communication over the I2C interface is conducted by sending the MSB of each byte of data first.

### 4.6.1 Set Power Save Mode with I2C Interface

Depending on the load current, in order to provide the best efficiency over the complete load range, the device works in PWM mode at load currents of approximately 250mA or higher. At lighter loads, the device switches automatically into Power Save Mode to reduce power consumption and extend battery life. The FPWM bit[3] of register 0x01 is used to select between the two different operation modes. To enable Power Save Mode, the bit must be set 0. Set this bit 1 to force PWM.

#### 4.6.2 Set Ultrasonic Mode with I2C Interface

The switching frequency decreases when it is very light load and it enters audio frequency that causes acoustic noise. To limit the minimal switching frequency, Ultrasonic mode is required. Write 1 to Ultra-Sonic bit[4] of register 0x01 to force it enable Ultrasonic function, the minimal switching frequency is 60kHz at no load.

#### 4.6.3 Ramp-PWM Operation (RPWM)

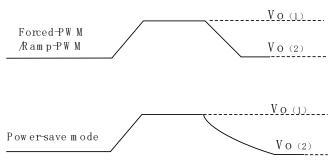

If Ramp-PWM operation is enabled, the device operates in forced-PWM when it ramps from one output voltage to another during dynamic voltage scaling. This function is useful if the device is needed to operate in power-save mode, but at the same time make sure that dynamic voltage scaling ramps the output voltage up and down in a controlled way. If the device operates in power-save mode and Ramp-PWM is disabled, the device cannot always control the ramp from a higher output voltage to a lower output voltage, because in power-save mode the device cannot sink current (see Figure 23).

To enable Ramp-PWM operation, set the RAMP bit in the Control register to 1. To disable Ramp-PWM operation, clear the RAMP bit in the Control register to 0.

Figure 23 Ramp-PWM Operation

### 4.6.4 Digital Slew Rate Control

When changing voltages using the I2C interface, the Au8310 can be programmed to control the slew rate of voltage increase or decrease as it transits from one voltage setting to the next. Details about the digital slew rate settings can be found in Table .

### 4.7 Register Map

Au8310 has five I2C accessible registers which include CONTROL Register, STATUS Register, DEVID Register, VOUT1 Register and VOUT2 Register. The registers are volatile: they lose their contents if the voltage on the VIN pin becomes less than 1.45V(typical) or a low logic level is applied to the EN pin.

### 4.7.1 CONTROL Register (Address = 0x01) [Default = 0x20]

This register configures the device.

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                    |  |  |  |  |  |

|-----|-------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | RESERVED    | R    | 0b    | Reserved                                                                                                                                                                       |  |  |  |  |  |

| 6   | RANGE       | R/W  | 0b    | This bit selects the output voltage range.<br>0b = Low range (1.800V to 4.975V)<br>1b = High range (2.025V to 5.200V)                                                          |  |  |  |  |  |

| 5   | ENABLE      | R/W  | 1b    | This bit enables and disables the output of Au8310.<br>0b = Output is disabled<br>1b = Output is enabled                                                                       |  |  |  |  |  |

| 4   | Ultra-Sonic | R/W  | 0b    | This bit controls ultrasonic mode.<br>0b=Ultrasonic mode disabled<br>1b=Ultrasonic mode enabled                                                                                |  |  |  |  |  |

| 3   | FPWM        | R/W  | Ob    | This bit controls forced-PWM operation.<br>0b=Forced-PWM operation disabled<br>1b=Forced-PWM operation enabled                                                                 |  |  |  |  |  |

| 2   | RPWM        | R/W  | 0b    | This bit controls ramp-PWM operation.                                                                                                                                          |  |  |  |  |  |

| 1-0 | SLEW        | R/W  | 00b   | The two bits control the slew rate of the converter when the output<br>voltage setting is changed to a new value.<br>00b=1.0V/ms<br>01b=2.5V/ms<br>10b=5.0V/ms<br>11b=10.0V/ms |  |  |  |  |  |

Table 12 CONTROL Register Field Descriptions

NOTE: R/W=Read/Write; R=Read only

### 4.7.2 STATUS Register (Address = 0x02) [Default = 0x00]

This register contains the device status. A read operation to this register clears the status bits.

| Bit | Field    | Туре | Reset  | Description                                                                                                                                                                                                                              |

|-----|----------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-2 | RESERVED | R    | 00000b | Reserved                                                                                                                                                                                                                                 |

| 1   | TSD      | R    | Ob     | This bit shows the status of the thermal shutdown function. This<br>bit is cleared if the STATUS register is read when the over<br>temperature condition no longer exists.<br>0b=Temperature good                                        |

|     |          |      |        | 1b=An over temperature event was detected                                                                                                                                                                                                |

| 0   | PG       | R    | Ob     | This bit shows the status of the output power good comparator.<br>This bit is cleared if the STATUS register is read when the power-<br>not- good condition no longer exists.<br>0b=Power good<br>1b=A power-not-good event was detected |

#### **Table 13 STATUS Register Field Descriptions**

NOTE: R/W=Read/Write; R=Read only

### 4.7.3 DEVID Register (Address = 0x03) [Default = 0xD0]

This register identifies the die revision of the device.

| Bit | Field        | Туре | Reset | Description                                                                                                                                                               |

|-----|--------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | MANUFACTURER | R    | 1101b | These bits identify the device manufacturer.                                                                                                                              |

| 3-2 | MAJOR        | R    | 00b   | The two bits identify the major die revision.<br>00b=A (initial silicon)<br>01b=B(first major revision)<br>10b=C(second major revision)<br>11b=D (third major revision)   |

| 1-0 | MINOR        | R    | 00b   | The two bits identify the minor die revision.<br>00b=0 (initial silicon)<br>01b=1 (first minor revision)<br>10b=2 (second minor revision)<br>11b=3 (third minor revision) |

#### Table 14 DEVID Register Field Descriptions

NOTE: R/W=Read/Write; R=Read only

### 4.7.4 VOUT1 Register (Address = 0x04) [Default = 0x3C]

This register sets the device output voltage when the VSEL pin is low.

#### Table 15 VOUT1 Register Field Descriptions

| Field    | Туре    | Reset     | Description                                                                                                                                                                                                                                                                                   |

|----------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED | R       | 0b        | Reserved                                                                                                                                                                                                                                                                                      |

| /OUT1    | R/W     | 0111100b  | These bits set the output voltage of the converter when the VSEL<br>pin is low.<br>The output voltage in volts is $1.8+(VOUT1[6:0] \times 0.025)$ (RANGE<br>bit =0b) (default =3.3V)<br>The output voltage in volts is $2.025+(VOUT1[6:0] \times 0.025)$<br>(RANGE bit =1b) (default =3.525V) |

| R        | ESERVED | ESERVED R | ESERVED R Ob                                                                                                                                                                                                                                                                                  |

NOTE: R/W=Read/Write; R=Read only

### 4.7.5 VOUT2 Register (Address = 0x05) [Default = 0x42]

This register sets the device output voltage when the VSEL pin is high.

| Bit | Field    | Туре | Reset    | Description                                                                                           |

|-----|----------|------|----------|-------------------------------------------------------------------------------------------------------|

| 7   | RESERVED | R    | 0b       | Reserved                                                                                              |

|     |          |      |          | These bits set the output voltage of the converter when the VSEL pin is high.                         |

| 6-0 | VOUT2    | R/W  | 1000010b | The output voltage in volts is 1.8+(VOUT2[6:0] × 0.025) (RANGE bit =0b) (default =3.45V)              |

|     |          |      |          | The output voltage in volts is $2.025+(VOUT2[6:0] \times 0.025)$<br>(RANGE bit =1b) (default =3.675V) |

#### Table 16 VOUT2 Register Field Descriptions

NOTE: R/W=Read/Write; R=Read only

#### 4.8 Programming

#### 4.8.1 Serial Interface Description

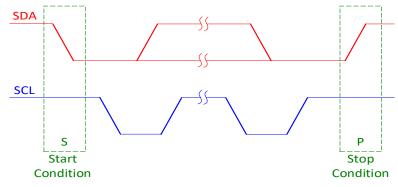

I2C is a 2-wire serial interface developed by Philips Semiconductor, now NXP Semiconductors (see UM10204: I2C-Bus Specification and User Manual, Revision 6). The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is idle, both SDA and SCL lines are pulled high. All the I2C- compatible devices connect to the I2C bus through open drain I/O pins, SDA and SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus under control of the master device.

The device works as a slave and supports the following data transfer modes, as defined in the I2C-Bus Specification: Standard-mode (100 kbps), Fast-mode (400 kbps) and Fast-mode Plus (1 Mbps). The interface adds flexibility to the power supply solution, enabling most functions to be programmed to new values depending on the instantaneous application requirements. Register contents remain intact as long as supply voltage remains above 2.2V.

The data transfer protocol for standard and fast modes is exactly the same, therefore it is referred to as F/Smode in this document. The device supports 7-bit addressing; 10-bit addressing and general call address are not supported. The device 7-bit address is 75h (1110101b).

To make sure that the I2C function in the device is correctly reset, it is recommended that the I2C master initiates a STOP condition on the I2C bus after the initial power up of SDA and SCL pull-up voltage.

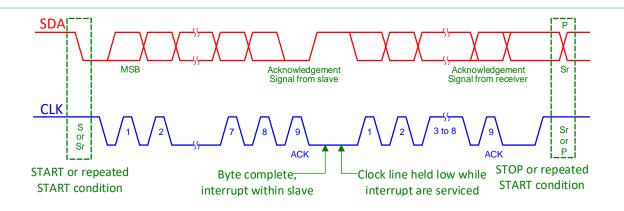

#### 4.8.2 Standard-, Fast-, Fast-Mode Plus Protocol

The master initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 24. All I2C-compatible devices should recognize a start condition.

Figure 24 START and STOP Conditions

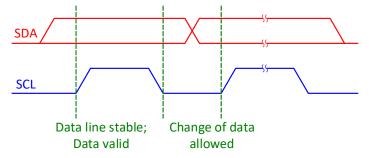

The master then generates the SCL pulses, and transmits the 7-bit address and the read/write direction bit R/W on the SDA line. During all transmissions, the master ensures that data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 25). All devices recognize

the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an acknowledge (see Figure26) by pulling the SDA line low during the entire high period of the ninth SCL cycle. Upon detecting this acknowledge, the master knows that communication link with a slave has been established.

Figure 25 Bit Transfer on the Serial Interface

The master generates further SCL cycles to either transmit data to the slave (R/W bit1) or receive data from the slave (R/W bit 0). In either case, the receiver needs to acknowledge the data sent by the transmitter. So an acknowledge signal can either be generated by the master or by the slave, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary. To signal the end of the data transfer, the master generates a stop condition by pulling the SDA line from low to high while the SCL line is high. This releases the bus and stops the communication link with the addressed slave. All I2C compatible devices must recognize the stop condition. Upon the receipt of a stop condition, all devices know that the bus is released, and they wait for a start condition followed by a matching address.

Attempting to read data from register addresses not listed in this section will result in 00h being read out.

Figure 26 Acknowledge on I2C Bus

Figure 27 Bus Protocol

#### 4.8.3 I2C Update Sequence

A single update requires a start condition, a valid I2C slave address, a register address, and a data byte. To acknowledge the receipt of each byte, the device pulls the SDA line low during the high period of a single clock pulse. The device performs an update on the falling edge of the acknowledge signal that follows the last byte.

| 1 | 7                                                                                                                                                                                                                                |      | 1   | . 1          | 8                  |       |           | 1      |       | 8      |              | 1       | 1   |   |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------|--------------------|-------|-----------|--------|-------|--------|--------------|---------|-----|---|--|

| S | S hve addre                                                                                                                                                                                                                      | ss   | R 🗡 | W A R        | egistera           | ıddre | ss        | А      | ]     | ) a ta |              | A ∕Ā    | Р   |   |  |

|   | From master to shave $A = A \operatorname{cknow} \operatorname{kedge}(SDA \operatorname{Low})$ $\overline{A} = A \operatorname{cknow} \operatorname{kedge}(SDA \operatorname{High})$ $S = START condition$                       |      |     |              |                    |       |           |        |       |        |              |         |     |   |  |

|   | From shve to masterS=START conditionP=STOP condition                                                                                                                                                                             |      |     |              |                    |       |           |        |       |        |              |         |     |   |  |

|   | Figure 28 Write Data Transfer Format in Standard, Fast and Fast-Plus Modes                                                                                                                                                       |      |     |              |                    |       |           |        |       |        |              |         |     |   |  |

|   |                                                                                                                                                                                                                                  |      |     | _            |                    |       |           |        |       |        | _            |         |     |   |  |

| 1 | 7                                                                                                                                                                                                                                | 1    | 1   | 8            | 1                  | 1     |           | 7      | 1     | 1      | 8            |         | 1   | 1 |  |

| S | Shve address                                                                                                                                                                                                                     | R ∕₩ | А   | Registeraddr | <mark>ess A</mark> | Sr    | S la ve a | addres | s R 📈 | А      | Data         | ι       | A 🗡 | Р |  |

|   | From master to slave $A = A \operatorname{cknow} \operatorname{kdge}(\operatorname{SDA} \operatorname{Low})$ $\overline{A} = A \operatorname{cknow} \operatorname{kdge}(\operatorname{SDA} \operatorname{H} \operatorname{igh})$ |      |     |              |                    |       |           |        |       |        |              |         |     |   |  |

|   |                                                                                                                                                                                                                                  |      |     |              |                    |       |           |        | _     | Ack    | nowledge (SI | A High) |     |   |  |

### **5** Application and Implementation

#### Note

Information in the following applications sections is not part of the Ningbo Aura Semiconductor component specification and Ningbo Aura Semiconductor does not warrant its accuracy or completeness. Ningbo Aura Semiconductor's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **5.1** Application Information

The Au8310 device is a highly integrated synchronous buck-boost DC/DC converter. This device is used to convert a wide range input voltage to a wide DC output voltage.

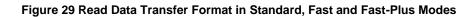

### 5.2 Typical Application

The application schematic of Figure 30 was developed to meet the requirements above. This circuit is available as the Au8310 evaluation module. The design procedure is given in this section.

### 5.3 Inductor Selection

Use an inductor with high frequency core material (for example, ferrite core) to minimize core losses and provide good efficiency. The inductor must be able to handle the peak switching currents without saturating.

A 0.47 µH inductor is recommended. Select an inductor with low DCR and low core losses to provide good efficiency. In applications in which radiated noise must be minimized, a toroidal or shielded inductor can be used. The saturation current of the inductor must be greater than the maximum inductor current in your application. To include sufficient margin for worst-case and transient operating conditions, and inductor with saturation current that is at least 20% higher than the maximum inductor current in your application. The maximum inductor occurs when the device operates in boost mode and the following is true:

- The input voltage is at its minimum value.

- The output voltage is at its maximum value.

- The output current is at its maximum value.

To calculate the maximum inductor current, first use Equation1 to calculate the maximum duty cycle during boost operation (which is when the maximum inductor current occurs).

$$D = \frac{VOUT - VIN}{VOUT}$$

Equation1

Where D is the duty cycle, VIN is the input voltage, VOUT is the output voltage. When VOUT=5V, VIN=2.5V,

$$D = \frac{5 - 2.5}{5} = 0.5$$

Then use Equation2 to calculate the maximum inductor current.

$$ILM = \frac{Io}{\eta(1-D)} + \frac{DVIN}{2fL}$$

Equation2

Where ILM is the peak inductor current, Io is the output current,  $\eta$  is the converter efficiency(assume 90%), f is the switching frequency(2.5MHz),L is the inductance(0.47 $\mu$ H).

So

$$LM = \frac{2}{0.9(1-0.5)} + \frac{0.5*2.5}{2*2.5M*0.47\mu} = 5A$$

Based on the above calculation, following inductors on Table17 are recommended to use.

| Vendor    | Part Number   | Description                         | Dimension (mm) | Website           |

|-----------|---------------|-------------------------------------|----------------|-------------------|

| Coilcraft | XFL4015-471ME | 0.47μH,20%, DCR=7.6mΩ,<br>Isat=5.4A | 4x4x1.5        | www.coilcraft.com |

| Toko      | DFE201612E    | 0.47μH,20%, DCR=26mΩ,<br>Isat=5.6A  | 2.0x1.6x1.2    | www.toko.com      |

| Wurth     | 784383340047  | 0.47μH,20%,DCR=26.4mΩ,<br>Isat=9A   | 3.0x3x1.2      | www.we-online.com |

#### T-61.401 . . . . ...

### 5.4 VIN and VOUT Capacitor Selection

The input and output capacitors should be ceramic X5R or X7R type with low ESL and ESR. The recommended input capacitor value is 2x10µF. A 0.1µF is also necessary to filter high frequency noise in input. The recommended Vo capacitor value is 2x22µF.

| Manufacture | Series  | Website                   |

|-------------|---------|---------------------------|

| Murata      | X5R/X7R | www.murata.com            |

| Taiyo Yuden | X5R/X7R | www.t-yuden.com           |

| TDK         | X5R/X7R | www.tdk.com               |

| Wurth       | X5R/X7R | https://www.we-online.com |

#### **Table 18 Capacitor Vendor Information**

#### Layout 6

#### 6.1 Layout Guidelines

- Layout is a critical portion of good power supply design. See Figure 31 for a PCB layout example.

- The top layer contains the main power traces for VIN, Vo, LX1 and LX2. Also on the top layer are • connections for the remaining pins of the Au8310 and a large top-side area filled with ground.

- There are several signals paths that conduct fast changing currents or voltages that can interact with stray • inductance or parasitic capacitance to generate noise or degrade the power supplies performance. To help eliminate these problems, the VIN pin should be bypassed to ground with a low ESR ceramic bypass capacitor with X5R or X7R dielectric.

- Care should be taken to minimize the loop area formed by the bypass capacitor connections, the VIN pins, • and the ground connections.

- Since the LX1 and LX2 connection are the switching node, the output inductor should be located close to the LX1 and LX2 pins, and the area of the PCB conductor minimized to prevent excessive capacitive coupling.

- The output filter capacitor ground should use the same power ground trace as the VIN input bypass capacitor.

- Try to minimize this conductor length while maintaining adequate width.

## 6.2 Layout Example

Figure 31 Layout Example

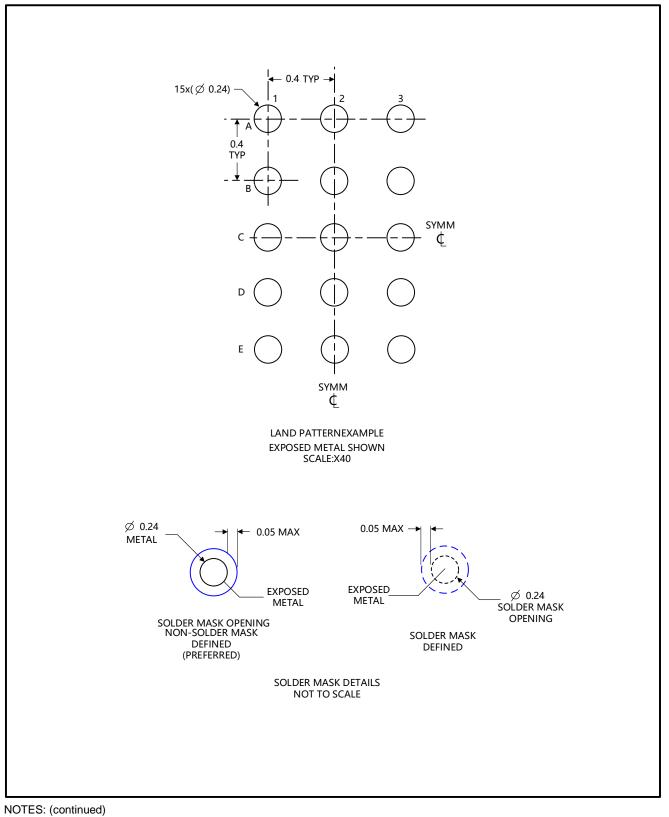

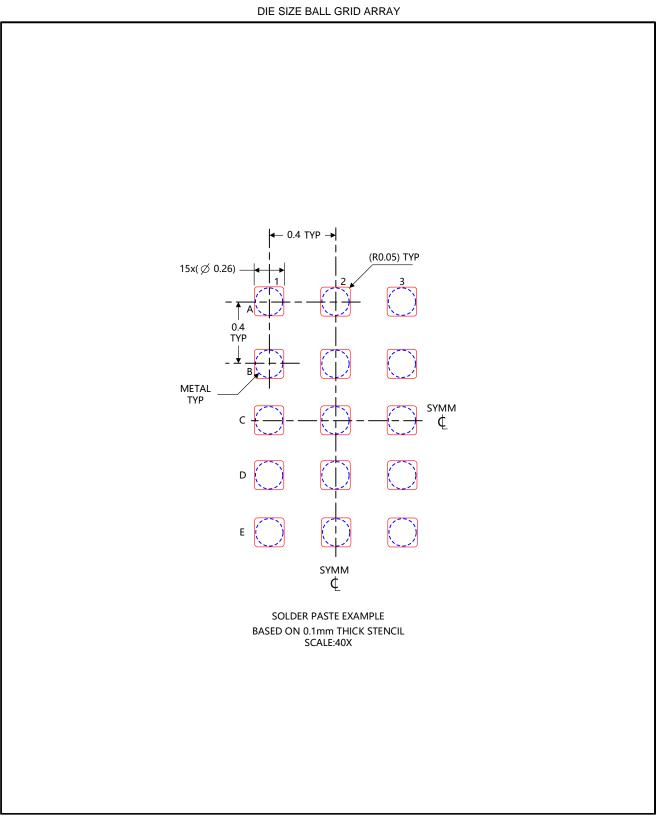

### 7 Package Outline Drawing

DIE SIZE BALL GRID ARRAY

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only.

- 2. This drawing is subject to change without notice.

DIE SIZE BALL GRID ARRAY

3. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints.

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

# 8 Revision History

| Version<br>Number | Date                        | Description                                                                                        | Author |

|-------------------|-----------------------------|----------------------------------------------------------------------------------------------------|--------|

| 0.1               | 2nd , July 2019             | Advanced Datasheet created                                                                         |        |

| 0.2               | 20th , Aug 2019             | Add layout guide and key feature description                                                       |        |

| 0.3               | 30th, Oct 2019              | Add I2C function description                                                                       |        |

| 0.4               | 8th, Nov 2019               | Updated the EC table                                                                               |        |

| 0.5               | 25th, Dec 2019              | Add ultrasonic mode, add by pass mode into register, update efficiency curve.                      |        |

| 0.6               | 05th, Jan 2020              | Add ultrasonic mode, remove by pass mode, update efficiency curve.                                 |        |

| 0.7               | 14th , Mar 2020             | Add DVS function description and control diagram, soft-start/<br>PG function                       |        |

| v0p1_FR 1.0       | 18th ,Apr 2020              | Add more figures                                                                                   |        |